Microcontrollori MCS-51: modello software, struttura, comandi. Microcontrollori MCS-51: modello di programma, struttura, comandi Microcontrollori della famiglia mcs 51

La base del microcontrollore (vedi Fig. 1) è un'unità logica aritmetica (ALU) a 8 bit. La memoria dell'MK ha un'architettura di Harvard, ad es. suddiviso logicamente: in memoria di programma - PP (interna o esterna), indirizzata da un contatore di comandi (SC) a 16 bit e memoria dati - interna (Memoria dati residente - RPD) 128 (o 256), nonché esterna (Esterna memoria dati – VPD) fino a 64 KB. Fisicamente, la memoria del programma è implementata su ROM (sola lettura) e la memoria dati è implementata su RAM (i dati possono essere scritti e letti).

La ricezione e la consegna dei segnali esterni avviene tramite 4 porte a otto bit Р0..Р3. Quando si accede alla memoria di programma esterna (EPM) o alla memoria dati (VPD), le porte P0 e P2 vengono utilizzate come bus indirizzi/dati esterno multiplexato. Le linee di porta P3 possono anche svolgere funzioni alternative (vedi Tabella 1).

Il registro DPTR a 16 bit costituisce l'indirizzo VPD o l'indirizzo di base della memoria di programma nell'istruzione di conversione dell'accumulatore. Il registro DPTR può essere utilizzato anche come due registri indipendenti a 8 bit (DPL e DPH) per memorizzare gli operandi.

Il registro di comando interno (RK) a 8 bit riceve il codice del comando in esecuzione; questo codice viene decodificato dal circuito di controllo, che genera segnali di controllo (vedi Fig. 1).

L'accesso ai registri di funzioni speciali - RSF (SFR - in Fig. 1 sono cerchiati con una linea tratteggiata) è possibile solo utilizzando l'indirizzamento a byte diretto nell'intervallo di indirizzi da 128 (80h) e oltre.

La memoria dati residente (RDD) nei primi modelli di microcontrollori della famiglia MCS-51 aveva una capacità di 128 byte. Anche i 32 byte inferiori dell'RPD sono registri generici - RON (4 banchi da 8 RON ciascuno). Il programma può essere applicato ad uno degli 8 RON della banca attiva. La selezione del banco di RON attivo viene effettuata programmando due bit nel registro di stato del processore - PSW.

Tabella 1 - Assegnazione dei pin dell'MCS-51

| Pin n. | Designazione | Scopo |

| 1..8 | P1 | Porta I/O quasi bidirezionale a 8 bit |

| 9 | RST | Segnale di ripristino (livello attivo - alto); Il segnale RST azzera: il PC e la maggior parte dei Registri di Funzioni Speciali (SFR), disabilitando tutti gli interrupt ei timer; seleziona Banco RON 0; scrive "tutti quelli" sulle porte P0_P3, preparandole per l'input; scrive il codice 07H nello stack pointer (SP); |

| 10..17 | Porta I/O quasi bidirezionale a 8 bit; dopo aver scritto nel bit corrispondente "1" - esegue funzioni aggiuntive (alternative): Ingresso porta seriale - RxD; Uscita porta seriale - TxD; Ingresso interrupt esterno 0 - ~INT0; Ingresso interrupt esterno 1 - ~INT1; Ingresso timer/contatore 0 - T0; Ingresso timer/contatore 1 - T1; Uscita stroboscopica. segnale durante la scrittura sul VPD - ~ WR; Uscita stroboscopica. segnale durante la lettura dal VPD - ~ RD; |

|

| 18, 19 | X1, X2 | Conclusioni per il collegamento di un risonatore al quarzo o di un circuito LC; |

| 20 | GND | Conclusione generale; |

| 21..28 | P2 | Porta I/O quasi bidirezionale a 8 bit; o indirizzo di uscita A in modalità memoria esterna (VPP o VPD); |

| 29 | PME | Strobo di lettura della memoria di programma esterna, emesso solo quando si accede a ROM esterna; |

| 30 | ALE | Strobe indirizzo memoria esterna (VPP o VPD); |

| 31 | EA | Disattivando l'RPP, il livello "0" a questo ingresso commuta l'MK su una selezione di comandi solo dalla pista ; |

| 39..32 | P0 | Porta I/O bidirezionale a 8 bit; quando accede alla memoria esterna, emette gli indirizzi A (che vengono scritti in un registro esterno dal segnale ALE), quindi scambia un byte in modo sincrono con il segnale ~PME (per comandi) o ~WR,~RD (per dati in VPD) , quando si accede alla Memoria Esterna tutte le unità vengono scritte nel registro di porta P0, distruggendo le informazioni ivi memorizzate; |

| 40 | Ucc | Uscita tensione di alimentazione |

La commutazione dei banchi di RON semplifica l'esecuzione di subroutine e la gestione degli interrupt, perché. non è necessario trasferire il contenuto dei RON del programma principale nello stack quando si chiama il sottoprogramma (è sufficiente passare ad un altro banco RON attivo nel sottoprogramma).

L'accesso all'RPD è possibile utilizzando l'indirizzamento a byte diretto o indiretto (l'indirizzamento a byte diretto consente di accedere solo ai primi 128 byte dell'RPD).

L'area RPD estesa (per i microcontrollori della famiglia MCS-52 e successive) dall'indirizzo 128 (80h) al 255 (FFh) può essere indirizzata solo utilizzando il metodo di indirizzamento indiretto.

Tabella 2 - Registri a blocchi delle funzioni speciali (s f r)

| Codice mnemo | Nome | |

| 0E0h | *ACC | Batteria |

| 0F0h | *B | Registra l'espansore batteria |

| 0D0h | *PSW | Parola di stato del processore |

| 0B0h | * P3 | Porta 3 |

| 0A0h | * P2 | Porta 2 |

| 90 ore | * P1 | Porta 1 |

| 80 ore | *P0 | Porta 0 |

| 0B8h | * IP | Registro di priorità di interruzione |

| 0A8h | *CIOÈ | Registro maschera di interruzione |

| 99 ore | SBUF | Buffer del ricetrasmettitore seriale |

| 98 ore | * SCON | Registro di controllo/stato della porta seriale |

| 89 ore | TMOD | Registro modalità timer/contatore |

| 88 ore | * TCON | Registro timer/contatore/stato |

| 8Dh | TH1 | Timer 1 (byte alto) |

| 8bh | TL1 | Timer 1 (byte basso) |

| 8 can | TH0 | Timer 0 (byte alto) |

| 8ah | TL0 | Timer 0 (byte basso) |

| 83 ore | DPH | Registro puntatore dati (DPTR) (byte alto) |

| 82 ore | DPL | Registro puntatore dati (DPTR) (byte basso) |

| 81h | SP | Registro del puntatore dello stack |

| 87 ore | PCON | Registro di controllo della potenza della domanda |

2. MODELLO SOFTWARE MCS–51

TIPI DI COMANDO MCS–51

Quasi la metà dei comandi viene eseguita in 1 ciclo macchina (MC). Con una frequenza dell'oscillatore a cristallo di 12 MHz, il tempo di esecuzione per tale comando è di 1 μs. I restanti comandi vengono eseguiti in 2 cicli macchina, ad es. per 2 ms. Solo le istruzioni di moltiplicazione (MUL) e divisione (DIV) vengono eseguite in 4 cicli macchina.

Durante un ciclo macchina, ci sono due accessi alla memoria di programma (interna o esterna) per leggere due byte dell'istruzione, oppure un accesso alla memoria dati esterna (EDM).

3. METODI (METODI) PER INDIRIZZARE MCS–51

1. INDIRIZZO DEL REGISTRO - L'operando a 8 bit si trova nel RON del banco di registri selezionato (attivo);

2 INDIRIZZO DIRETTO (indicato dal segno - #) - l'operando si trova nel secondo (e per un operando a 16 bit e nel terzo) byte del comando;

3 INDIRIZZO INDIRETTO (indicato dal segno - @) - l'operando è nella Memoria Dati (RPD o VPD), e l'indirizzo della cella di memoria è contenuto in uno dei RON dell'indirizzamento indiretto (R0 o R1); nei comandi PUSH e POP l'indirizzo è contenuto nello stack pointer SP; il registro DPTR può contenere un indirizzo VPD fino a 64K;

4 DIRECT BYTE ADDRESSING – (dir) – utilizzato per accedere alle celle RPD (indirizzi 00h…7Fh) e ai registri di funzioni speciali SFR (indirizzi 80h…0FFh);

5 INDIRIZZO DIRETTO A BIT - (bit) - viene utilizzato per indirizzare 128 bit indirizzabili separatamente situati nelle celle RPD agli indirizzi 20H ... 2FH ea bit indirizzabili separatamente di registri di funzioni speciali (vedere Tabella 3 e modello di programma);

6 INDIRIZZO INDIRETTO INDICE (indicato dal segno @) - semplifica la visualizzazione delle tabelle nella memoria di programma, l'indirizzo PP è determinato dalla somma del registro di base (PC o DPTR) e del registro di indice (Batteria);

7 INDIRIZZO IMPLICITO (INCORPORATO) - il codice dell'istruzione contiene un riferimento implicito (di default) a uno degli operandi (il più delle volte all'Accumulatore).

4. FORMATO WORD DI STATO DEL PROCESSORE (PSW).

C - Carry (CARY) o prendere in prestito flag, funziona anche come un "accumulatore booleano" nelle istruzioni a bit;

AC - flag di riporto ausiliario (aggiuntivo) - impostato su "1" se il comando di addizione (ADD, ADDC) ha avuto un riporto dalla tetrade di ordine basso all'ordine alto (cioè dal 3° bit al 4° bit);

F0 - flag utente - impostato, resettato e verificato da software;

| RS1 | RS0 | Banca | Indirizzo (dir) |

| 0 | 0 | 0 | 00h..07h |

| 0 | 1 | 1 | 08h..0Fh |

| 1 | 0 | 2 | 10h..17h |

| 1 | 1 | 3 | 18h..1Fh |

RS1,RS0 – Selezione banca registro:

OV - Flag di overflow aritmetico; il suo valore è determinato dall'operazione XOR dei segnali di riporto in ingresso e in uscita del bit più significativo dell'ALU; un singolo valore di questo flag indica che il risultato di un'operazione aritmetica nel codice del complemento a due è fuori intervallo: –128…+127; quando si esegue l'operazione di divisione, il flag OV viene azzerato e, in caso di divisione per zero, viene impostato; durante la moltiplicazione viene impostato il flag OV se il risultato è maggiore di 255 (0FFH);

Bit PSW - Riservato, contiene un trigger, disponibile per la scrittura o la lettura;

P - flag di parità - è la somma del numero di singoli bit nell'accumulatore a un numero pari; è formato da un circuito combinatorio (programmaticamente disponibile solo per la lettura).

I microcontrollori MCS-51 non hanno il flag "Z". Ma nelle istruzioni di salto condizionale (JZ, JNZ), il circuito combinatorio controlla il contenuto corrente (zero o diverso da zero) dell'accumulatore.

Tutti i comandi di trasferimento e scambio di operandi possono essere eseguiti tramite l'Accumulatore (vedi Fig. 3). Inoltre, i trasferimenti da/a Memoria Esterna (Memoria Programmi o Memoria Dati) possono essere effettuati solo attraverso la Batteria.

La maggior parte dei trasferimenti può essere effettuata anche tramite un byte forward (dir). Ci sono anche trasferimenti da directory a directory (vedi Figura 3).

I trasferimenti mancanti da RON a RON possono essere implementati come trasferimenti da RON alla directory del byte forward (dato che i RON si trovano nell'area iniziale della Resident Data Memory, le cui celle possono essere indirizzate come dir).

I comandi di scambio XCH consentono di inviare byte senza distruggere entrambi gli operandi.

I comandi aritmetici vengono eseguiti solo nell'Accumulatore. Pertanto, il primo operando deve essere prima posizionato nell'Accumulatore e quindi aggiungere o sottrarre il secondo operando. Il risultato viene inserito nell'Accumulatore.

Il comando di sottrazione SUBB viene eseguito solo con un prestito (ovvero, dal risultato viene sottratto anche il flag Cary). Pertanto, per eseguire un'istruzione di sottrazione senza prendere in prestito, è necessario eseguire prima l'istruzione Clear Flag C (CLRC).

L'istruzione per moltiplicare gli operandi a un byte - MULAB - pone un risultato a due byte (16 bit): il byte basso è nell'accumulatore, il byte alto è nel registro B.

Il risultato dell'esecuzione dell'istruzione per la divisione degli operandi a un byte - DIVAB - viene posto: il quoziente - un Accumulator, il resto - nel registro B.

L'istruzione aritmetica INC ne aggiunge uno all'operando selezionato. L'istruzione aritmetica DEC ne sottrae uno dall'operando selezionato. L'istruzione Accumulator Decimal Correction (DAA) consente di aggiungere numeri decimali codificati binari (BCD) senza convertirli in formato esadecimale (esadecimale). Gli operandi di origine devono essere in formato BCD, ad es. in ogni tetrade di un byte ci sono solo numeri da 0 a 9 (non possono esserci numeri esadecimali: A, B, C, D, E, F). Pertanto, un byte può contenere numeri da 00 a 99 per numeri BCD compressi o numeri da 0 a 9 per numeri BCD non compressi.

Il comando DA A - correzione decimale esegue azioni sul contenuto dell'Accumulatore dopo aver aggiunto i numeri BCD nel processore (i numeri sono stati aggiunti secondo le leggi dell'aritmetica esadecimale) come segue (vedi esempio):

· se il contenuto della tetrade di ordine inferiore dell'Accumulatore è maggiore di 9 o è impostato il flag di riporto ausiliario (AC = 1), al contenuto dell'Accumulatore viene aggiunto 6 (cioè le sei cifre mancanti in esadecimale formato);

· se successivamente il contenuto dell'ordine superiore dell'Accumulatore è maggiore di 9 o viene impostato il flag C, all'ordine superiore dell'Accumulatore viene aggiunto il numero 6.

L'istruzione di correzione decimale DA A non viene utilizzata dopo l'istruzione di incremento (INC) perché l'istruzione di incremento non influisce (modifica) i flag C e AC.

Comandi logici:

"AND" logico - ANL,

"OR" logico - ORL,

Il comando logico XOR - XRL - viene eseguito nell'Accumulatore (oltre che aritmetico), ma è possibile eseguire comandi logici anche nel byte di indirizzo diretto (dir). In questo caso, il secondo operando può essere:

nella batteria o

Un operando immediato in un'istruzione.

Le istruzioni di rotazione (RR A, RL A) e le istruzioni di rotazione tramite il flag CARY (RRC A, RLC A) ruotano il contenuto dell'Accumulatore di 1 bit Gli operandi di bit vengono inviati solo tramite il flag C.

L'architettura della famiglia MCS-51 è in gran parte predeterminata dal suo scopo: la costruzione compatto e a buon mercato dispositivi digitali. Tutte le funzioni del microcomputer sono implementate utilizzando un singolo microcircuito. La famiglia MCS-51 comprende un'intera gamma di microcircuiti, dai microcontrollori più semplici a quelli piuttosto complessi. I microcontrollori della famiglia MCS-51 consentono di eseguire sia le attività di controllo di vari dispositivi sia l'implementazione di singoli nodi del circuito analogico. Tutti i microcircuiti di questa famiglia funzionano allo stesso modo sistema di comando MCS-51, la maggior parte di essi viene eseguita negli stessi casi con piedinatura corrispondente(numerazione delle gambe per il caso). Ciò ti consente di utilizzare chip di diverse aziende per il dispositivo sviluppato: Maxim, Atmel, NXP, ecc. (catalog..php?page=components_list&id=39"> s.m. Ricerca per parametri) senza alterare lo schema elettrico del dispositivo e del programma.

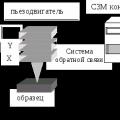

Figura 1. Schema a blocchi del controller I8751

Lo schema a blocchi del controllore è mostrato in Figura 1 ed è costituito dalle seguenti unità funzionali principali: un'unità di controllo, un'unità logica aritmetica, un'unità timer/contatore, un'interfaccia seriale e un'unità di interrupt, un contatore di programmi, memoria dati e memoria di programma. Lo scambio bilaterale viene effettuato utilizzando un'autostrada dati interna a 8 bit.

Diamo un'occhiata più da vicino allo scopo di ogni blocco. Quasi tutti i rappresentanti della famiglia MCS-51 sono costruiti secondo questo schema.. Vari microcircuiti di questa famiglia differiscono solo nei registri per scopi speciali (compreso il numero di porte). Sistema di comando di tutti i controller della famiglia MCS-51 contiene 111 comandi di base con un formato di 1, 2 o 3 byte e non cambia quando si passa da un chip all'altro. Ciò fornisce un'eccellente portabilità dei programmi da un chip all'altro.

Unità di controllo e sincronizzazione

L'unità di controllo e sincronizzazione (Timing and Control) è progettata per generare segnali di sincronizzazione e controllo che assicurano il coordinamento del funzionamento congiunto delle unità OEVM in tutte le modalità consentite del suo funzionamento.L'unità di controllo comprende:

- - dispositivo per la formazione di intervalli di tempo,

- - Logica I/O,

- - registro delle istruzioni,

- - registro di gestione dei consumi elettrici,

- - decodificatore di comando, logica di controllo del computer.

Dispositivo di fascia orariaè destinato alla generazione e all'uscita di segnali di sincronizzazione interni di fasi, cicli e cicli. Il numero di cicli macchina determina la durata dell'esecuzione dell'istruzione. Quasi tutti i comandi OEVM vengono eseguiti in uno o due cicli macchina, ad eccezione delle istruzioni di moltiplicazione e divisione, la cui durata è di quattro cicli macchina. Indichiamo la frequenza dell'oscillatore principale con F g. Quindi la durata del ciclo macchina è 12/F g, ovvero 12 periodi del segnale dell'oscillatore principale. La logica input-output è progettata per ricevere ed emettere segnali che garantiscono lo scambio di informazioni con dispositivi esterni attraverso le porte input/output P0-P3.

Registro di comandoè progettato per registrare e memorizzare un codice operativo a 8 bit del comando in esecuzione. Il codice operativo, con l'ausilio di un decodificatore di comandi e di una logica di controllo del computer, viene convertito in un microprogramma per l'esecuzione dei comandi.

Registro di controllo della domanda (PCON) consente di interrompere il funzionamento del microcontrollore per ridurre il consumo energetico e ridurre il livello di interferenza del microcontrollore. Una riduzione ancora maggiore del consumo energetico e della riduzione del rumore può essere ottenuta arrestando l'oscillatore principale del microcontrollore. Ciò può essere ottenuto commutando i bit nel registro di controllo della domanda PCON. Per l'opzione di produzione n-MOS (serie 1816 o chip stranieri che non hanno la lettera "c" al centro del nome), il registro di controllo dell'alimentazione PCON contiene un solo bit che controlla il baud rate della porta seriale SMOD, e non ci sono bit di controllo della potenza.

Unità logica aritmetica (ALU)è un dispositivo parallelo a otto bit che fornisce operazioni aritmetiche e logiche. L'ALU è composta da:

- - registri accumulatori, registri di memoria temporanea TMP1 e TMP2,

- - costanti ROM,

- - sommatore,

- - registro aggiuntivo (registro B),

- - accumulatore (ACC),

- - registro dello stato del programma (PSW).

Registrati batteria e registri di detenzione- registri a otto bit atti a ricevere e memorizzare operandi per la durata delle operazioni su di essi. Questi registri non sono accessibili a livello di codice.

costanti ROM assicura lo sviluppo di un codice di correzione per la rappresentazione dei dati binari-decimali, un codice maschera per le operazioni di bit e un codice costante.

Sommatore parallelo a 8 bitè un circuito combinatorio a trasferimento sequenziale, progettato per eseguire operazioni aritmetiche di addizione, sottrazione e operazioni logiche di addizione, moltiplicazione, disparità e identità.

Registro B- un registro a otto bit utilizzato durante le operazioni di moltiplicazione e divisione. Per altre istruzioni, può essere considerato come un ulteriore registro scratchpad.

Batteria- un registro a otto bit atto a ricevere e memorizzare il risultato ottenuto durante l'esecuzione di operazioni aritmetico-logiche o operazioni di spostamento

Interfaccia seriale e blocco di interrupt (SIP)è progettato per organizzare l'input-output di flussi di informazioni sequenziali e organizzare il sistema di interrupt di programma. Il blocco comprende:

- - Buffer PIP,

- - logica di controllo,

- - registro di controllo,

- - buffer del trasmettitore,

- - buffer del ricevitore,

- - ricetrasmettitore per porta seriale,

- - registro di priorità di interruzione,

- - registro di abilitazione interruzione,

- - logica per l'elaborazione dei flag di interrupt e uno schema di generazione del vettore.

Contatore di programmaè progettato per formare l'indirizzo corrente a 16 bit della memoria di programma interna e l'indirizzo a 8/16 bit della memoria di programma esterna. Il contatore del programma è costituito da un buffer PC a 16 bit, un registro PC e un circuito di incremento (contenuto incrementale di 1).

Memoria dati (RAM)è destinato alla memorizzazione temporanea delle informazioni utilizzate durante l'esecuzione del programma.

Porte P0, P1, P2, P3 sono porte input-output quasi bidirezionali e sono progettate per garantire lo scambio di informazioni tra OEVM e dispositivi esterni, formando 32 linee input-output.

Dispositivo timer I modelli base della famiglia dispongono di due timer/contatori programmabili a 16 bit (T/C0 e T/C1) utilizzabili sia come timer che come contatori eventi esterni.

Registro dello stato del programma (PSW)è progettato per memorizzare informazioni sullo stato dell'ALU durante l'esecuzione del programma.

Memoria di programma (EPROM) progettato per memorizzare programmi ed è una memoria di sola lettura (ROM). Vari microcircuiti utilizzano ROM mascherate che vengono cancellate dalle radiazioni ultraviolette o VELOCE ROM.

Registro puntatore dati (DPTR)è progettato per memorizzare l'indirizzo a 16 bit della memoria dati esterna o della memoria di programma.

Puntatore stack (SP)è un registro a otto bit progettato per organizzare una speciale area di memoria dati (stack) in cui qualsiasi cella di memoria può essere temporaneamente archiviata.

Lo stato del sistema di interrupt viene interrogato al termine di ogni ciclo macchina nella fase S5P2, ad eccezione delle istruzioni RETI e di eventuali istruzioni che accedono ai registri IE e IP. Occorrono da 38 a 86 periodi di frequenza fOSC dal momento in cui la richiesta di interruzione è impegnata a servire l'interruzione, a seconda della fase della richiesta e del numero di cicli macchina dell'istruzione durante i quali è stata ricevuta la richiesta.

Quando l'interrupt è implementato nell'hardware, viene eseguita l'istruzione LCALL addr16, che assicura che lo stato corrente del contatore del programma sia memorizzato nello stack (memorizzazione dell'indirizzo di ritorno) e il passaggio all'indirizzo iniziale addr16 della procedura di servizio corrispondente è eseguita. Ogni sorgente di richiesta di interruzione ha la propria associata

indirizzo iniziale (vettore di interruzione): |

||||

Interruzione esterna INT0. |

||||

Interruzione temporizzata/contatore TC0. |

||||

Interruzione esterna INT1. |

||||

Interruzione temporizzata/contatore TC1. |

||||

Interruzione della porta seriale. |

||||

2.7. Metodi di indirizzamento e sistema di comando della famiglia MCS-51

Il sistema di comando della famiglia MCS-51 è focalizzato sull'organizzazione di input/output dati flessibili attraverso porte universali P0...P3 e sull'elaborazione delle informazioni primarie. Particolare attenzione è riservata alle operazioni con i bit e al trasferimento del controllo in base al loro valore. Le istruzioni che eseguono tali operazioni formano un grande gruppo e, insieme all'hardware corrispondente, formano il cosiddetto "processore booleano" come parte dell'architettura MCS-51.

Il sistema di comando offre al programmatore la possibilità di utilizzare la maggior parte delle operazioni con una serie completa di metodi di indirizzamento e risorse hardware accessibili tramite software.

2.7.1. Metodi di indirizzamento

Ogni istruzione indica al processore l'operazione da eseguire ei metodi per accedere agli operandi. Il codice di comando ha diversi campi che hanno uno scopo funzionale specifico. I campi più importanti di qualsiasi comando sono il codice operazione (COP), che determina l'azione del comando, e la parte dell'indirizzo. I campi della parte indirizzo contengono informazioni sugli indirizzi degli operandi e sul risultato dell'operazione e, in alcuni casi, informazioni sull'indirizzo dell'istruzione successiva.

Se l'indirizzo punta al numero della cella di memoria in cui si trova l'operando o in cui è stato immesso, viene chiamato indirizzo diretto.

I metodi di indirizzamento sono un insieme di meccanismi per accedere agli operandi. Alcuni di essi sono semplici, risultando in un formato di istruzione compatto e un rapido accesso all'operando, ma hanno una quantità limitata di risorse disponibili. Altri consentono di operare con tutte le risorse disponibili nel sistema, ma il comando risulta essere lungo,

l'input e l'esecuzione sono spesi molto tempo. L'insieme dei metodi di indirizzamento in ciascun insieme di istruzioni è una combinazione di compromesso di noti meccanismi di indirizzamento scelti dai progettisti di architettura in base all'insieme di compiti da risolvere.

Di seguito sono riportati i principali metodi di indirizzamento utilizzati nel sistema di comando della famiglia MCS-51.

Indirizzamento implicito. Il comando non contiene indicazioni esplicite circa l'indirizzo dell'operando partecipante all'operazione o l'indirizzo a cui è posto il risultato dell'operazione, ma questo indirizzo è implicito. Nei comandi, l'accumulatore è spesso implicitamente indirizzato come destinazione del risultato di un'operazione. Ad esempio, il risultato della somma del contenuto dell'accumulatore (A) e del registro R1 della banca dati corrente mediante l'istruzione ADD A,R1 viene scritto nell'accumulatore indirizzato implicitamente. L'intera istruzione specificata occupa un byte di memoria, mentre l'indirizzo del solo accumulatore (8Eh dell'area SFR) contiene un byte.

Indirizzamento diretto. Nel campo dell'indirizzo del comando, contiene

Non è l'indirizzo dell'operando che vive, ma l'operando stesso. L'indirizzamento diretto è indicato dal carattere speciale # prima del numero. Ad esempio, il comando MOV A,#15h carica il numero esadecimale 15 (il secondo byte del comando) nell'accumulatore. Nel sistema di comando, l'indirizzamento diretto è indicato come #dati, dove dati è un numero

(dati = 00h...FFh).

Indirizzamento diretto. Il campo dell'indirizzo dell'istruzione specifica l'indirizzo diretto della locazione di memoria dati in cui si trova l'operando o dove è scritto. Ad esempio, l'istruzione MOV A,15h carica il contenuto della cella DSEG all'indirizzo 15h nell'accumulatore. La cella di memoria è indirizzabile direttamente, mentre l'accumulatore è indirizzato implicitamente. A seconda della posizione dell'operando indirizzato, l'indirizzamento diretto è suddiviso in indirizzamento diretto del registro e indirizzamento assoluto.

Indirizzamento diretto del registro. Il campo dell'indirizzo del comando contiene l'indirizzo del registro diretto della banca di registro corrente. Ci sono otto registri in ogni banca e per indirizzarli è necessario un indirizzo diretto a tre bit. Nella mnemonica del comando, il registro indirizzabile è indicato con Rn, dove n=0...7. Tutti i campi del comando sono contenuti in un byte. Tale indirizzamento è chiamato breve. Ad esempio, MOV R4, R1.

Indirizzamento assoluto diretto consente di accedere a qualsiasi cella DSEG e area SFR. L'indirizzo diretto in questo caso richiede un byte e il comando richiede due byte. Nel sistema di comando, il byte di indirizzo diretto è indicato dalla parola direct (direct) (direct = 00h ... FFh). Ad esempio, l'istruzione MOV 80h,R2 (o MOV P0,R2) carica il contenuto del registro R2 della banca dati corrente nella porta P0 (posizione 80h dell'SFR). Se entrambi gli operandi sono indirizzabili assoluti direttamente, l'istruzione diventa un'istruzione a tre byte (ad es. MOV 80h,15h).

indirizzamento indiretto. Il campo dell'indirizzo contiene l'indirizzo della locazione di memoria in cui si trova l'indirizzo diretto dell'operando. Nel sistema di comando, l'indirizzamento indiretto è indicato dal carattere speciale @. proprietà

i registri R0 e R1 (@Ri, i = 0.1) di ciascuna banca registri devono memorizzare l'indirizzo diretto. Ad esempio, se il contenuto del registro R1 del banco di registri corrente è 15h, l'istruzione MOV A,@R1 eseguirà la stessa azione dell'istruzione MOV A,15h sopra - caricherà il contenuto della posizione di memoria DSEG con indirizzo 15h nell'accumulatore. Tuttavia, il comando MOV A, @ R1 è di un byte, ma soprattutto è possibile modificare l'indirizzo a livello di codice modificando il contenuto del registro R1.

Indirizzamento relativo. Con l'indirizzamento relativo, l'indirizzo diretto viene formato sommando l'indirizzo di base al campo indirizzo del comando. Il contenuto del contatore del programma viene utilizzato come indirizzo di base e il campo dell'indirizzo dell'istruzione è un offset rel (relativo) di otto bit. Il numero rel viene interpretato dal comando come un intero con segno rappresentato in complemento a due. La sua gamma di presentazione è (-128...+127). Quando si determina il numero rel, tenere presente che il contatore del programma punta all'istruzione successiva da eseguire. L'indirizzamento relativo è ampiamente utilizzato nei comandi di trasferimento del controllo, che consente la creazione di moduli di programma rilocabili. I comandi di trasferimento del controllo con relativo indirizzamento consentono la diramazione relativa alla posizione attuale del contatore del programma del PC in entrambe le direzioni di (-128...+127) byte.

Nei programmi in linguaggio assembly, il campo offset può essere utilizzato per specificare l'etichetta a cui passare. Come risultato della traslazione, l'assemblatore calcolerà il valore di offset se non supera (-128…+127). In caso contrario, verrà emesso un messaggio di errore.

Indirizzamento di base rappresenta una sorta di indirizzamento relativo. L'indirizzo diretto in questo caso si forma sommando l'indirizzo specificato nel comando al contenuto del registro di base, che memorizza l'indirizzo di base. La funzione del registro di base nella famiglia MCS-51 viene eseguita dal registro del puntatore di dati DPTR o dal contatore del programma del PC. Questo tipo di indirizzamento è particolarmente utile durante l'elaborazione di tabelle e array di dati. Nelle istruzioni MOVC A,@A+DPTR e MOVC A,@A+PC, l'indirizzo diretto a 16 bit è formato dalla somma del contenuto dei registri DPTR e A o PC e A.

Indirizzamento delle pagine. Quando si utilizza l'indirizzamento delle pagine, la memoria è suddivisa in un numero di pagine della stessa lunghezza. L'indirizzamento delle pagine viene eseguito da un registro di pagina separato e le celle di memoria all'interno di una pagina vengono indirizzate dall'indirizzo contenuto nell'istruzione. L'indirizzo diretto è formato concatenando (allegando) l'indirizzo delle pagine e l'indirizzo della cella di memoria all'interno della pagina. Nell'istruzione MOVX A,@Ri, la porta P2 (byte alto dell'indirizzo) svolge la funzione di registro della pagina e il contenuto del registro Ri (byte basso dell'indirizzo) specifica l'indirizzo all'interno della pagina. In questo caso, la memoria è suddivisa in 256 pagine di 256 celle in ciascuna di esse.

Indirizzamento dello stack utilizzato nei comandi senza indirizzo ed è una combinazione di metodi di indirizzamento con incremento e decremento automatico, che operano secondo il principio LIFO (Last I nput - First O utput) - "last in - first out". Lo stack si trova in DSEG e cresce nella direzione dell'indirizzo crescente. L'indirizzo della parte superiore dello stack è contenuto nel puntatore dello stack SP. Quando un byte viene inserito nello stack, il contenuto di SP viene prima incrementato e quindi viene scritto l'indirizzo. Quando si legge un byte dallo stack, leggere prima all'indirizzo indicato da SP, quindi decrementare SP. Quando si utilizza uno stack, tenere presente che la profondità dello stack (il numero massimo di celle di memoria occupate dallo stack) non è controllata dall'hardware. Con un aumento eccessivo dello stack, le celle di memoria non destinate ad esso possono essere occupate con la perdita di informazioni in esse. Lo stack hardware viene utilizzato per memorizzare l'indirizzo di ritorno durante la manutenzione di un interrupt.

2.7.2. Sistema di comando della famiglia MCS-51

Il sistema di comando è presentato nelle Tabelle A2.1...A2.6 dell'Appendice 2. Le tabelle mostrano il nome del comando, il suo mnemonico, il codice operativo binario, l'effetto del comando eseguito sui flag C, OV, AC e P, la lunghezza del comando in byte (B) e il tempo di esecuzione in cicli macchina (C), nonché il contenuto della conversione eseguita dall'istruzione. Una virgola viene utilizzata come separatore per i campi degli indirizzi nei comandi. Per migliorare la leggibilità, è possibile aggiungere spazi dopo la virgola se supportati dall'assembler utilizzato.

L'intero set di comandi può essere suddiviso in 5 gruppi: operazioni di trasferimento dati, operazioni aritmetiche, operazioni logiche, operazioni con bit e operazioni di trasferimento di controllo.

Gruppo comando operazione di trasferimento dati(Tabella A2.1) co-

contiene MOV (trasferimento dati tra DSEG e RSEG), MOVC (tra CSEG e A), MOVX (tra XSEG e A), comandi di accesso allo stack PUSH e POP e due comandi di scambio XCH e XCHD. Tutte le istruzioni di trasferimento dati la cui destinazione è l'accumulatore impostano il flag di parità P del contenuto dell'accumulatore e le istruzioni di indirizzamento diretto la cui destinazione è il registro PSW cambiano tutti i flag. La più capiente è l'istruzione MOV, che utilizza quattro metodi di indirizzamento: registro diretto (A, Rn, DPTR), diretto (diretto), indiretto (@Ri), diretto (#data, #data16). Il secondo operando del comando è la sorgente, il primo operando è la destinazione. Esistono tre metodi di indirizzamento (tranne diretto) per specificare la destinazione e tutti e quattro per specificare l'origine. L'istruzione MOV direct,direct a tre byte fornisce un trasferimento tra due celle di memoria qualsiasi (DSEG e SFR), incluso RSEG. Per lo scambio con RSEG sono previsti formati speciali a due e un byte:

L'istruzione speciale MOV DPTR,#data16 carica un puntatore DPTR a 16 bit con il valore data16.

L'istruzione MOVC consente di leggere le informazioni dalla memoria del programma CSEG non nel registro dei comandi del dispositivo di controllo, ma nell'accumulatore del dispositivo di comando. Il comando utilizza due metodi di indirizzamento: basato su DPTR e relativo al PC. In entrambi i casi, l'offset intero senza segno (indice) viene memorizzato nell'accumulatore. L'accumulatore funge anche da ricevitore del risultato. Il comando consente di eseguire una rapida ricodifica per tabelle.

Si accede alla memoria esterna usando l'istruzione MOVX. Lo scambio avviene per byte tra l'accumulatore e l'XSEG esterno. Una cella XSEG può essere indirizzata in due modi: indirettamente tramite un puntatore DPTR a 16 bit e indirettamente per pagina tramite un puntatore Ri a 8 bit, i=0,1. In quest'ultimo caso, il registro delle pagine è P2.

I comandi PUSH e POP non indirizzati forniscono il trasferimento dei dati

tra DSEG, RSEG e SFR.

Il comando di scambio XCH fornisce uno scambio di byte a due vie e il comando XCHD fornisce le tetradi inferiori di operandi di byte.

Gruppo di istruzioni per operazioni aritmetiche(Tabella A2.2) co-

tiene Add ADD, Carry Add ADDC, Borrow Subtract SUBB, Increment and Decrement by One INC e DEC, Packed BCD Decimal Correction, Moltiply MUL e Divide DIV. Le operazioni vengono eseguite su numeri interi senza segno. Nelle operazioni di addizione e sottrazione, l'accumulatore è il primo operando e la destinazione del risultato. Il registro diretto, l'indirizzamento diretto assoluto, diretto e indiretto vengono utilizzati per definire il secondo operando. Le operazioni INC e DEC si applicano ad un accumulatore, un registro direttamente indirizzabile, una locazione di memoria indirizzabile direttamente o indirettamente. Inoltre, l'operazione INC si applica al contenuto del registro del puntatore DPTR a 16 bit.

La moltiplicazione di interi e le operazioni di divisione senza segno coinvolgono l'accumulatore e il registro B. Nella moltiplicazione, il valore a 8 bit di A viene moltiplicato per il valore a 8 bit di B e il risultato a 16 bit viene scritto nella coppia BA. In questo caso, il registro B memorizza la parte più alta del prodotto. Il flag OV viene impostato se il prodotto è maggiore di 255. Quando un valore A a 8 bit viene diviso per un valore B a 8 bit, il quoziente viene scritto in A e il resto in B. Un tentativo di dividere per 0 imposta il valore Flag di overflow OV.

Il comando di correzione decimale dell'accumulatore DA viene posto dopo il comando di addizione. I termini devono essere rappresentati in codice BCD. La correzione viene eseguita in modo standard.

Gruppo di istruzioni logiche(Tabella A2.3 ) contiene tre operazioni tipiche: ANL - AND logico, ORL - OR logico, XRL - OR logico esclusivo. Sorgente del primo operando

è l'accumulatore A o una cella di memoria direttamente indirizzabile. Il secondo operando è specificato da uno dei quattro metodi di indirizzamento di base. Il gruppo comprende anche singole operazioni sopra il contenuto dell'accumulatore: CLR - azzeramenti, CPL - inversioni, nonché RL, RLC, RR e RRC - operazioni di spostamenti ciclici ed estesi a destra e a sinistra. Ciò include anche l'operazione di scambio di tetradi nell'accumulatore SWAP, che può essere interpretato come uno spostamento ciclico di un byte di quattro bit.

Gruppo istruzioni operazione bit(tabella A2.6) contiene co-

comandi SETB - imposta un bit a 1, CLR - ripristina un bit a 0, CPL - inversione di bit, ANL e ORL - AND logico e OR logico del contenuto del flag C e un bit indirizzato direttamente, MOV - inoltro di bit.

v Nelle operazioni bit per bit, il flag C svolge il ruolo di accumulatore booleano. Il contenuto del flag C o il bit direttamente indirizzabile dell'area BSEG vengono utilizzati come operandi. Nelle operazioni ANL e ORL è possibile utilizzare il contenuto del bit (bit) indirizzato direttamente o l'inverso del contenuto (/bit).

v questo gruppo include anche istruzioni di salto condizionato con relativo Offset 8 bit rel. Un branch condizionale può essere eseguito sia quando il bit è impostato (comando JB) che azzerato (comando JNB). Di particolare rilievo è l'istruzione JBC, che, quando un bit è impostato, implementa un branch e contemporaneamente azzera il bit a 0.

Gruppo di comando di trasferimento di controllo(Tabelle A2.4 e A2.5)

contiene istruzioni di salto incondizionato AJMP, LJMP, SJMP, JMP, salto condizionale JZ, JNZ, CJNE, chiamata ACALL, LCALL, ritorno RET, RETI e aggiornamento con salto condizionale DJNZ. Anche il comando NOP vuoto è incluso qui.

v L'indirizzamento relativo è ampiamente utilizzato nei comandi di trasferimento del controllo per consentire la creazione di moduli di programma rilocabili. L'indirizzo relativo è L'offset a 8 bit rel è un byte con segno che fornisce una transizione a (-128… +127) byte rispetto alla posizione corrente del PC. È possibile utilizzare l'indirizzo addr16 diretto o l'indirizzo indiretto @A+DPTR per passare a qualsiasi altro punto nello spazio degli indirizzi di 64 KB. In quest'ultimo caso, il contenuto di A viene interpretato come un intero senza segno. Viene introdotta una variante dell'indirizzamento diretto breve addr11 all'interno della pagina corrente 2K per compatibilità con la famiglia MCS-48.

Tutti questi tipi di indirizzamento vengono utilizzati nelle istruzioni di salto. I comandi di chiamata utilizzano solo i metodi di indirizzamento addr16 diretti e addr11 in-page. Tutti i comandi condizionali utilizzano solo l'indirizzamento relativo.

Quando il microcontrollore riconosce una richiesta di interruzione, emette un'istruzione LCALL addr16, che memorizza automaticamente l'indirizzo di ritorno nello stack. Le informazioni sullo stato del programma (il contenuto del registro PSW) non vengono memorizzate automaticamente. in cui

UDC 681.5, 681.325.5 (075.8)

BBK 32.973.202-018.2 i 73

Shcherbina A. N.Macchine, sistemi e reti informatiche. Microcontrollori e microprocessori nei sistemi di controllo: Cheb. indennità / A.N. Shcherbina, PA Nechaev-SPb.: Dal Politecnico. un-ta, 2012.-226 p.

Corrisponde al contenuto dello standard educativo statale per aree di formazione e specialità nel campo della gestione dei sistemi tecnici, dell'energia elettrica e dell'ingegneria elettrica e al contenuto del curriculum esemplare della disciplina "Computer, sistemi e reti".

Le questioni fondamentali dell'organizzazione logica dei sistemi a microprocessore sono considerate sull'esempio dell'architettura di base della famiglia di microcontrollori MCS-51 di Intel. Viene descritta la tecnologia di programmazione dei microcontrollori nei linguaggi Assembler e SI.

Può essere utile per studenti e insegnanti di istituti tecnici superiori, specialisti nell'automazione di processi tecnologici e apparecchiature di produzione, nonché per ingegneri progettisti di sistemi a microprocessore.

Corrisponde inoltre al contenuto dello standard educativo statale delle discipline "Microcontrollori e microprocessori nei sistemi di controllo" e "Dispositivi elettronici di automazione" per la formazione di laurea, ingegneria e master nella direzione 140400 "Energia elettrica ed ingegneria elettrica".

Pubblicato per decisione del consiglio di redazione ed editoria

Università Politecnica Statale di San Pietroburgo.

© Shcherbina A.N., Nechaev P.A., 2012

© Stato di San Pietroburgo

Politecnico, 2012

ISBN 978-5-7422-3553-8

Introduzione.. 7

Capitolo 1. Architettura della famiglia MCS51. 10

1.1 Caratteristiche generali 10

1.2 Schema a blocchi 11

1.3 Assegnazione dei pin del microcontrollore 8051 15

1.4 Organizzazione della memoria 17

1.4.1 Memoria di programma (ROM) 18

1.4.2 Memoria dati (RAM) 19

1.4.3 Registri delle funzioni speciali. venti

1.4.4 Flag Register (PSW) 23

1.5 Dispositivo di controllo e sincronizzazione 26

1.6 Organizzazione delle porte I/O 27

1.6.1 Informazioni generali. 27

1.6.2 Funzioni alternative. 27

1.7. Temporizzatori/contatori di microcontrollori della famiglia 8051. 28

1.7.1. Struttura dei contatori-temporizzatori. 28

1.7.2 Modalità di funzionamento dei temporizzatori-contatori. trenta

1.8. Porta seriale 32

1.8.1. La struttura della porta seriale. 32

1.8.2. Registro di controllo/stato del ricetrasmettitore SCON.. 34

1.8.3. Registro di controllo della potenza PCON.. 36

1.9. Sistema di interruzione 37

1.9.1. La struttura del sistema di interrupt. 37

1.9.2 Esecuzione della routine di interrupt. 40

Capitolo 2 Caratteristiche del microcontrollore 80C51GB.. 42

2.1 Caratteristiche 42

2.2 Porte I/O P0-P5 43

2.2.1 Funzionamento delle porte I/O. 43

2.2.2 Scrittura sulla porta.. 46

2.3 Caratteristiche del sistema di interrupt 8XC51GB.. 49

Abilita/disabilita gli interrupt. 50

Interrompere la gestione delle priorità. 51

interruzioni esterne. 54

2.3. nodo ADC 56

2.4. Watchdog hardware 61

2.5. Rilevamento guasto orologio 63

2.6. Matrice di contatori programmabili RSA 64

2.6.1. Struttura PCA.. 64

2.6.2. Registro modalità contatore PCA (CMOD) 66

2.6.3. Registro di controllo del contatore PCA (CON) 67

2.6.4. Confronta/correggi i moduli. 68

2.7. Porta seriale avanzata 76

2.8. Timer/contatori 79

Assegnazione dei pin dei microcontrollori di gruppo 8XC51GB.. 86

Capitolo 3 Programmazione MK 8051GB.. 89

3.1. Modello software 89

3.2 Tipi di dati 93

3.3 Modalità di indirizzamento dei dati 93

3.4 Sistema di comando 95

3.4.1 Caratteristiche generali. 95

3.4.2 Tipi di comando. 96

3.4.3 Tipi di operandi. 97

3.4.4 Comandi di trasferimento dati del microcontrollore. 98

3.4.5 Istruzioni aritmetiche 8051.101

3.4.6 Comandi logici MCU 8051. 104

3.4.7 Comandi operativi 8051 bit. 106

3.5 Debug dei programmi 111

Capitolo 4. Linguaggio di programmazione ASM-51. 112

4.2 Scrittura del testo del programma 113

4.3 Alfabeto della lingua. 114

4.4 Identificatori. 115

4.5 Numeri 117

4.6 Direttive 118

4.7 Implementazione di subroutine in ASM51 122

4.7.1 La struttura della procedura di subroutine nel linguaggio ASM51. 122

4.7.2 Passaggio di variabili di parametro a una subroutine. 123

4.7.3 Implementazione di sottoprogrammi-funzioni in linguaggio ASM51. 123

4.7.4 Implementazione di routine di gestione degli interrupt nel linguaggio ASM51. 124

4.8 Programmazione strutturata in linguaggio assembly. 125

4.9 Peculiarità della traduzione di programmi multimodulo.. 126

4.10 Utilizzo dei segmenti 128

4.10.1 Partizionamento della memoria MK in segmenti .. 128

4.10.2 Segmenti di memoria assoluta. 129

4.10.2 Segmenti di memoria rilocabili. 131

Capitolo 5. Il linguaggio di programmazione C-51. 134

5.1 Caratteristiche generali della lingua 134

5.3 Struttura dei programmi C-51 136

5.3. Elementi del linguaggio di programmazione C-51 138

5.3.1. Simboli.. 138

5.3.2. Unità lessicali, separatori e uso degli spazi. 141

5.3.3 Identificatori.. 142

5.3.4 Parole chiave. 143

5.3.5 Costanti.. 143

5.4. Espressioni nelle dichiarazioni linguistiche 146

programmazione C-51 146

5.5. Priorità dell'operazione 148

5.6. C-51 dichiarazioni del linguaggio di programmazione 149

5.6.1. operatori di dichiarazione. 150

5.6.2 Dichiarazioni eseguibili.. 150

5.6.3 Operatore di assegnazione. 151

5.6.4 Enunciato condizionale. 151

5.6.5 Operatore strutturale (). 152

5.6.6 L'istruzione del ciclo for. 152

5.6.7 Istruzione di ciclo con controllo delle condizioni fino al corpo del ciclo while. 153

5.6.8 Istruzione di ciclo con controllo della condizione dopo che il corpo del ciclo fa while. 154

5.6.9 La dichiarazione di rottura. 155

5.6.10 L'istruzione continua. 155

5.6.11 Dichiarazione di selezione del cambio. 155

5.6.12 L'operatore goto. 157

5.6.13 Espressione dell'operatore. 158

5.6.14 Dichiarazione di ritorno dalla restituzione della subroutine. 158

5.6.15 Dichiarazione vuota. 158

5.7. Dichiarazione di variabili nel linguaggio di programmazione C-51. 159

5.7.1. Dichiarazione variabile. 159

5.7.3 Tipi di dati interi. 161

5.7.4 Numeri in virgola mobile. 162

5.7.5 Variabili di tipo enumerato. 162

5.7.6. Dichiarazione di array nel linguaggio di programmazione C-51. 164

5.7.7. Strutture.. 165

5.7.8. Associazioni (miscele) 166

5.8. Utilizzo dei puntatori in C-51 167

5.8.1. Dichiarando i puntatori. 167

5.8.2. Puntatori non digitati. 168

5.8.3. Puntatori dipendenti dalla memoria. 169

5.9. Dichiarazione di nuovi tipi di variabili 169

5.10. Inizializzazione dei dati 170

5.11. Utilizzo di subroutine nel linguaggio di programmazione C-51. 170

5.11.1. Definizione di sottoprogrammi.. 171

5.11.2. Parametri del sottoprogramma .. 173

5.11.3. Dichiarazione anticipata di sottoprogrammi.. 174

5.11.4 Chiamare subroutine.. 176

5.11.5 Richiamo ricorsivo di sottoprogramma.. 176

5.11.6 Routine di interruzione. 177

5.11.7 Ambito di variabili e subroutine.. 178

5.12. Programmi multimodulo 179

Capitolo 6. Preparazione dei programmi nell'ambiente di sviluppo integrato Keil μVision2. 182

6.1 Creazione di un progetto ASM-51 182

6.2 Esempio di creazione di un progetto C per un training controller in Keil μVision2 IDE 188

Capitolo 7 Descrizione del controller di apprendimento .. 199

7.1. Struttura del controllore 199

7.2. Spazio indirizzi 200

7.2.1. Allocazione della memoria. 200

7.2.2 Memoria esterna. 201

7.2.3. Memoria dati interna. 202

7.3. Allocazione porta I/O 202

7.4. Porta seriale…………………………………...203

7.5. Lavorare con LCD 205

7.6. Pannelli di controllo………………………………………………………213

APPENDICE P2 STRUTTURA DELLA RELAZIONE SUL LAVORO DI LABORATORIO……..217

Appendice P3 Codici dei comandi macchina. 217

Riferimenti... 224

introduzione

Nello sviluppo di specialità legate all'automazione dei processi tecnologici e della produzione, lo studio dei microcontrollori è una delle sezioni importanti.

C'è uno sviluppo continuo e l'emergere di un numero sempre maggiore di microcontrollori e microprocessori a 16 e 32 bit nel mondo, ma la quota maggiore del mercato mondiale dei microprocessori rimane ancora con i dispositivi a 8 bit. Secondo tutte le previsioni delle società di analisi per il prossimo futuro, la posizione di leadership dei microcontrollori a 8 bit nel mercato mondiale continuerà.

Attualmente, tra tutti i microcontrollori a 8 bit, la famiglia MCS-51 è il leader indiscusso per numero di varietà e numero di aziende che ne producono le modifiche. Prende il nome dal primo rappresentante di questa famiglia: il microcontrollore 8051. Un set di periferiche di successo, la possibilità di una scelta flessibile di memoria di programma esterna o interna e un prezzo accessibile hanno assicurato a questo microcontrollore un successo sul mercato.

Vantaggi della famiglia MCS-51:

architettura, che è lo standard de facto;

L'estrema ampiezza della famiglia e la varietà delle opportunità;

Disponibilità di versioni estese e ad alte prestazioni dei processori;

un numero significativo di sviluppi software e hardware liberamente disponibili;

facilità di programmazione hardware, inclusa la programmazione in-circuit;

basso costo e disponibilità di chip di base;

Disponibilità di versioni specializzate di controller per condizioni d'uso speciali

Disponibilità di versioni di controllori con un livello ridotto di interferenza elettromagnetica;

· ampia popolarità tra gli sviluppatori della vecchia generazione, sia nel mondo che nei paesi della CSI;

Sostegno all'architettura da parte delle principali istituzioni educative del mondo.

E, infine, il vantaggio principale: avendo padroneggiato il chip base della famiglia, è facile iniziare a lavorare con tali "mostri" informatici come Cygnal, Dallas Semiconductor, Analog Devices, microcontrollori Texas Instruments.

La famiglia MCS-51 comprende un'intera gamma di microcircuiti, dai microcontrollori più semplici a quelli piuttosto complessi. Ad oggi sono più di 200 le modifiche dei microcontrollori della famiglia 8051, prodotti da quasi 20 aziende. Ogni anno ci sono sempre più varianti di rappresentanti di questa famiglia.

Le principali aree di sviluppo sono:

aumento della velocità (aumento della frequenza di clock e ridisegno dell'architettura);

riduzione della tensione di alimentazione e del consumo di energia;

· aumento della quantità di memoria RAM e FLASH su chip con possibilità di programmazione in-circuit;

· introduzione di dispositivi complessi come sistemi di controllo drive, interfacce CAN e USB, ecc. nella periferia del microcontrollore.

I microcontrollori della famiglia MCS-51 consentono di eseguire sia le attività di controllo di vari dispositivi sia l'implementazione di singoli nodi del circuito analogico. Tutti i microcircuiti di questa famiglia funzionano con lo stesso sistema di comando. La maggior parte di essi viene eseguita negli stessi casi con la stessa piedinatura (numerazione delle gambe per il caso). Ciò consente di utilizzare microcircuiti di diversi produttori per il dispositivo sviluppato senza alterare lo schema elettrico del dispositivo e il programma.

I principali produttori di varietà della 51a famiglia nel mondo sono Philips, Siemens, Intel, Atmel, Dallas, Temic, Oki, AMD, MHS, Gold Star, Winbond, Silicon Systems e molti altri.

Le caratteristiche degli analoghi dei microcontrollori della famiglia MCS-51 (Intel 8XC51FA, 8XC51GB, 80C152) con funzionalità avanzate sono riportate nella tabella. IN 1.

Tabella B.1

| RAM | rom | SAR | ADC | WDT | T/C | Placenta. Canali | Peculiarità | |

| Atmosfera: AT89C2051 | ||||||||

| - | - | - | - | UART | Flash 2Kb | |||

| AT89C4051 | - | - | - | - | UART | Flash 4Kb | ||

| AT89S4D12 | 128K | - | - | - | UART, SPI | Flash 4Kb | ||

| DALLAS Semiconduttore: DS5000FP | ||||||||

| - | - | - | + | UART | caricatore di bootstrap | |||

| DS5001FP | - | - | - | + | UART | caricatore di bootstrap | ||

| DS8xC520 | 16K | - | - | + | 2xUART | 2DPTR | ||

| SIEMENS: C505C | ||||||||

| 16K | - | + | + | UART, CAN | 8DPTR | |||

| C515C | 64K | - | + | + | UART+SSC+CAN | 4 PWM, 8 DPTR | ||

| Philips: *89C51RA+ | ||||||||

| - | + | - | + | UART | 2 DPTR, lvl 4 interrupt, clock out, Flash 8K | |||

| P51XAG1x | 8 MILA | - | - | + | 2 UART | |||

| Intel: 8xC51RA | ||||||||

| 8 MILA | - | + | + | UART | 4 livelli IRQ, clock out | |||

| 8XC196KC | 64K | 16K | - | + | - | UART | 3 PWM | |

| 80C196KB | 64K | 8 MILA | - | + | - | UART | PWM |

Capitolo 1 Architettura della famiglia MCS51

I microcontrollori a chip singolo a 8 bit della famiglia MCS-51 hanno guadagnato grande popolarità tra gli sviluppatori di sistemi di controllo a microprocessore grazie alla loro architettura ben progettata. L'architettura del microcontrollore è un insieme di risorse hardware accessibili tramite software interne ed esterne e un sistema di comandi. L'architettura della famiglia MCS-51 è in gran parte determinata dal suo scopo: la costruzione di dispositivi digitali compatti ed economici. I microcontrollori che svolgono tutte le funzioni di un microcomputer utilizzando un singolo microcircuito sono chiamati computer a chip singolo (OEVM).

Intel ha rilasciato circa 50 modelli basati sul core operativo del microcontrollore Intel 8051. Allo stesso tempo, molte altre aziende, come Atmel, Philips, hanno iniziato la produzione dei loro microcontrollori sviluppati nello standard MCS-51.

Caratteristiche generali

Le principali caratteristiche della famiglia:

· Unità centrale di elaborazione (CPU) a 8 bit, focalizzata sul controllo dei dispositivi esecutivi;

· La CPU ha un circuito integrato di moltiplicazione hardware a 8 bit e divisione dei numeri;

La presenza nel set di istruzioni di un gran numero di operazioni per lavorare con bit direttamente indirizzabili consente di parlare di un processore per lavorare con dati a bit (processore booleano);

memoria di programma interna (on-chip) di tipo mask o riprogrammabile, che ha un volume da 4 a 32 Kb per vari cristalli, è assente in alcune versioni;

· almeno 128 byte di RAM residente dati, utilizzata per l'organizzazione, le banche registri, lo stack e l'archiviazione dei dati dell'utente;

· almeno 32 linee di interfaccia (porte) bidirezionali, configurate singolarmente per l'ingresso o l'uscita di informazioni;

· due contatori/temporizzatori multimodali a 16 bit utilizzati per contare gli eventi esterni, organizzare le temporizzazioni e sincronizzare la porta di comunicazione;

· Ricetrasmettitore asincrono duplex bidirezionale (UART) progettato per organizzare i canali di comunicazione tra il microcontrollore ei dispositivi esterni con un'ampia gamma di velocità di trasferimento delle informazioni. Esistono mezzi per l'integrazione hardware-software dei microcontrollori in un sistema connesso;

· un sistema di interrupt di priorità a due livelli che supporta almeno 5 vettori di interrupt da 4 sorgenti di eventi interne e 2 esterne;

generatore di clock integrato.

Schema strutturale

Lo schema a blocchi del controllore è mostrato nella Figura 1.1 ed è costituito dalle seguenti unità funzionali principali: un'unità di controllo, un'unità logica aritmetica, un'unità timer/contatore, un'interfaccia seriale e un'unità di interrupt, un contatore di programmi, una memoria dati e memoria di programma. Lo scambio bilaterale viene effettuato utilizzando un'autostrada dati interna a 8 bit. Quasi tutti i rappresentanti della famiglia MCS-51 sono costruiti secondo questo schema. Vari microcircuiti di questa famiglia differiscono solo nei registri per scopi speciali (compreso il numero di porte).

Unità di controllo e sincronizzazione (Temporizzazione e Controllo)- progettato per generare segnali di sincronizzazione e controllo che garantiscano il coordinamento del funzionamento congiunto delle unità OEVM in tutte le modalità consentite del suo funzionamento. L'unità di controllo comprende:

dispositivo per formare intervalli di tempo;

logica ingresso-uscita;

registro delle istruzioni;

registro di gestione dei consumi elettrici;

decodificatore di comando, logica di controllo del computer.

Riso. 1.1. Schema strutturale del controller I8051.

Dispositivo di fascia orariaè destinato alla generazione e all'uscita di segnali di sincronizzazione interni di fasi, cicli e cicli. Il numero di cicli macchina determina la durata dell'esecuzione dell'istruzione. Quasi tutti i comandi OEVM vengono eseguiti in uno o due cicli macchina, ad eccezione delle istruzioni di moltiplicazione e divisione, la cui durata è di quattro cicli macchina. Indichiamo la frequenza dell'oscillatore master con F g. La durata del ciclo macchina è 12/F g, ovvero 12 periodi del segnale dell'oscillatore master. La logica input-output è progettata per ricevere ed emettere segnali che garantiscono lo scambio di informazioni con dispositivi esterni attraverso le porte input/output P0-P3.

Registro di comandoè progettato per registrare e memorizzare un codice operativo a 8 bit del comando in esecuzione. Il codice operativo, con l'ausilio di un decodificatore di comandi e di una logica di controllo del computer, viene convertito in un microprogramma per l'esecuzione dei comandi.

Registro di controllo della domanda (PCON) consente di interrompere il funzionamento del microcontrollore per ridurre il consumo energetico e ridurre il livello di interferenza del microcontrollore. Una riduzione ancora maggiore del consumo energetico e della riduzione del rumore può essere ottenuta arrestando l'oscillatore principale del microcontrollore. Ciò può essere ottenuto commutando i bit nel registro di controllo della domanda PCON. Per l'opzione di produzione n-MOS (serie 1816 o chip stranieri che non hanno la lettera "c" al centro del nome), il registro di controllo dell'alimentazione PCON contiene un solo bit che controlla il baud rate della porta seriale SMOD, e non ci sono bit di controllo della potenza.

Unità logica aritmetica (ALU)è un dispositivo parallelo a otto bit che fornisce operazioni aritmetiche e logiche. L'ALU è composta da:

registri ad accumulatore, registri di detenzione TMP1 e TMP2;

costanti ROM;

sommatore;

registro aggiuntivo (registro B);

batteria (ACC);

registro dello stato del programma (PSW).

Registrati accumulatori e registri di partecipazione- registri a otto bit atti a ricevere e memorizzare operandi per la durata delle operazioni su di essi. Questi registri non sono accessibili a livello di codice.

costanti ROM assicura lo sviluppo di un codice di correzione per la rappresentazione dei dati binari-decimali, un codice maschera per le operazioni di bit e un codice costante.

Sommatore parallelo a 8 bitè un circuito di tipo combinatorio a trasferimento sequenziale, progettato per eseguire operazioni aritmetiche di addizione, sottrazione e operazioni logiche di addizione, moltiplicazione, inequivalenza e identità.

Registro B- un registro a otto bit utilizzato durante le operazioni di moltiplicazione e divisione. Per altre istruzioni, può essere considerato come un ulteriore registro scratchpad.

Batteria- un registro a otto bit atto a ricevere e memorizzare il risultato ottenuto durante l'esecuzione di operazioni aritmetico-logiche o operazioni di spostamento

Interfaccia seriale e blocco di interrupt (SIP) progettato per organizzare l'input - output di flussi informativi sequenziali e l'organizzazione del sistema di interrupt di programma. Il blocco comprende:

buffer PIP;

logica di controllo;

registro di controllo;

buffer del trasmettitore;

buffer del ricevitore;

ricetrasmettitore per porta seriale;

registro di priorità di interruzione;

registro di abilitazione interruzione;

logica di elaborazione del flag di interruzione e schema di generazione del vettore.

Contatore di programmaè progettato per formare l'indirizzo corrente a 16 bit della memoria di programma interna e l'indirizzo a 8/16 bit della memoria di programma esterna. Il contatore del programma è costituito da un buffer PC a 16 bit, un registro PC e un circuito di incremento (contenuto incrementale di 1).

Memoria dati (RAM)è destinato alla memorizzazione temporanea delle informazioni utilizzate durante l'esecuzione del programma.

Porte P0, P1, P2, P3 sono porte input-output quasi bidirezionali e sono progettate per garantire lo scambio di informazioni tra OEVM e dispositivi esterni, formando 32 linee input-output.

Registro dello stato del programma (PSW)è progettato per memorizzare informazioni sullo stato dell'ALU durante l'esecuzione del programma.

Memoria di programma (EPROM) progettato per memorizzare programmi ed è una memoria di sola lettura (ROM). Vari microcircuiti utilizzano ROM mascherate, cancellabili con UV o FLASH.

Registro puntatore dati (DPTR) progettato per memorizzare un indirizzo a 16 bit di memoria dati esterna.

Puntatore stack (SP)è un registro a otto bit progettato per organizzare una speciale area di memoria dati (stack), in cui è possibile memorizzare temporaneamente qualsiasi cella di memoria.

1.3 Assegnazione dei pin del microcontrollore 8051(Fig. 1.2)

· U ss - il potenziale del filo comune ("terra");

U cc - tensione di alimentazione principale +5 V;

· X1,X2 - conclusioni per il collegamento di un risuonatore al quarzo;

· RST - ingresso del reset generale del microcontrollore;

PSEN - autorizzazione alla memoria del programma esterna, rilasciata solo quando si accede alla ROM esterna;

· ALE - strobo indirizzo memoria esterna;

· EA - disabilita la memoria interna del programma; il livello 0 a questo ingresso fa sì che il microcontrollore esegua il programma solo dalla ROM esterna; ignorare l'interiore (se quest'ultimo esiste);

Riso. 1.2. Assegnazione dei pin 8051.

P1 - porta di ingresso/uscita quasi bidirezionale a otto bit, ogni bit della porta può essere programmato sia per l'ingresso che per l'uscita di informazioni, indipendentemente dallo stato degli altri bit;

· P2 - una porta quasi bidirezionale a otto bit, simile a P1, i pin di questa porta vengono utilizzati per inviare informazioni sull'indirizzo quando si accede a un programma esterno o alla memoria dati (se viene utilizzato l'indirizzamento a 16 bit di quest'ultima). Inoltre, i pin delle porte vengono utilizzati durante la programmazione per inserire i bit di ordine superiore dell'indirizzo nel microcontrollore;

R3: una porta quasi bidirezionale a otto bit, simile a P1, i pin di questa porta possono eseguire una serie di funzioni alternative utilizzate nel funzionamento dei timer, una porta I/O seriale, un controller di interrupt e un programma esterno e memoria dati;

· P0 - porta bidirezionale multiplexata a otto bit di input-output di informazioni, attraverso questa porta in diversi momenti vengono emessi il byte basso dell'indirizzo e dei dati.

Organizzazione della memoria

L'intera serie MCS-51 ha un'architettura Harvard, ovvero programmi separati e spazi di indirizzi di memoria dati. La struttura della memoria è mostrata in fig. 1.3.

La quantità di memoria di programma interna (residente) (ROM, EPROM o OTP ROM) che si trova su un chip, a seconda del tipo di microcircuito, può essere 0 (ROMless), 4K (chip di base), 8K, 16K o 32K. Se necessario, l'utente può espandere la memoria del programma installando una ROM esterna. L'accesso alla ROM interna o esterna è determinato dal valore del segnale al pin EA (External Access):

EA=V cc (tensione di alimentazione) - accesso alla ROM interna;

EA=V ss (potenziale di terra) - accesso a ROM esterna.

Per i chip ROMless, il pin EA deve essere collegato permanentemente a V ss .

|  |

Riso. 1.3. Organizzazione della memoria della famiglia MCS-51

Strobe di lettura ROM esterna - (Program Store Enable) viene generato quando si accede alla memoria del programma esterna ed è inattivo durante l'accesso alla ROM situata sul chip. L'area di indirizzo della memoria di programma insufficiente viene utilizzata dal sistema di interrupt. L'architettura del chip di base 8051 supporta cinque sorgenti di interrupt:

due interrupt esterni;

due interruzioni da timer;

interrupt dalla porta seriale.

Sulla fig. 1.4 mostra una mappa dell'area inferiore della memoria di programma.

Riso. 1.4. Mappa dell'area inferiore della memoria di programma

Memoria di programma (ROM)

Per i microcontrollori della famiglia 8051, la memoria di programma e la memoria dati sono dispositivi indipendenti e indipendenti, indirizzati da vari comandi e segnali di controllo.

La quantità di memoria di programma integrata situata sul chip del microcontrollore 8051 è di 4 KB (nella famiglia fino a 32). Quando si accede alla memoria di programma esterna, tutti i microcontrollori 8051 utilizzano sempre un indirizzo a 16 bit, che fornisce loro l'accesso a 64 KB di ROM. Il microcontrollore accede alla memoria del programma durante la lettura del codice operativo e degli operandi (utilizzando il contatore del programma del PC), nonché durante l'esecuzione dei comandi per copiare un byte dalla memoria del programma all'accumulatore. Quando si eseguono comandi di copia dei dati, l'indirizzamento della cella di memoria del programma da cui verranno letti i dati può essere effettuato utilizzando sia il contatore del PC che uno speciale registro DPTR a puntatore dati a due byte.

Memoria dati (RAM)

La quantità di memoria dati su chip è di 128 byte. La memoria dati esterna può arrivare fino a 64 KB. I primi 32 byte sono organizzati in quattro banchi di registri di uso generale, denominati rispettivamente banco 0 - banco 3. Ciascuno di essi è costituito da otto registri R0-R7. In ogni momento il programma ha a disposizione, con indirizzamento dei registri, un solo banco di registri, il cui numero è contenuto nel terzo e quarto bit della word di stato del programma PSW.

8051 Indirizzi dell'area dei bit del microcontrollore

Tabella 1.1

| Indirizzo byte (esadecimale) | Indirizzi bit per bit | |||||||

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

| 2F | 7F | 7E | 7D | 7C | 7B | 7A | ||

| 2E | ||||||||

| 2D | 6F | 6E | 6D | 6C | 6B | 6A | ||

| 2C | ||||||||

| 2B | 5F | 5E | 5 D | 5C | 5B | 5A | ||

| 2A | ||||||||

| 4F | 4E | 4D | 4C | 4B | 4A | |||

| 3F | 3E | 3D | 3C | 3B | 3A | |||

| 2F | 2E | 2D | 2C | 2B | 2A | |||

| 1F | 1E | 1D | 1C | 1B | 1A | |||

| 0F | 0E | 0D | 0C | 0B | 0A | |||

| 20h |

Lo spazio di indirizzi rimanente può essere configurato dallo sviluppatore a propria discrezione: può ospitare le aree dello stack, del sistema e dei dati dell'utente. È possibile accedere alle celle di memoria dati in due modi. Il primo modo è l'indirizzamento diretto di una cella di memoria. In questo caso, l'indirizzo di cella è l'operando dell'istruzione corrispondente. Il secondo metodo è l'indirizzamento indiretto tramite registri puntatori R0 o R1: prima di eseguire il comando corrispondente, uno di essi deve contenere l'indirizzo della cella a cui si vuole accedere.

Per accedere alla memoria dati esterna, viene utilizzato solo l'indirizzamento indiretto utilizzando i registri R0 e R1 o utilizzando il registro puntatore a 16 bit DPTR.

Parte della memoria dati è un'area di bit, ha la capacità di utilizzare comandi bit speciali per indirizzare ogni cifra delle celle di memoria. L'indirizzo dei bit direttamente indirizzabili può essere scritto anche nella forma (ByteAddress).(Bit). La corrispondenza tra questi due metodi di indirizzamento può essere determinata dalla tabella. 1.1.