マイクロプロセッサシステムの設計。 マイクロプロセッサデバイスの設計のための設計プログラムの主な段階

デバイスのブロック図を付録Aに示します。

このマイクロプロセッサシステムは、マイクロプロセッサ、RAM、ROM、プログラム可能なパラレルインターフェイス、アナログ-デジタルコンバータ、タイマー、ディスプレイのブロックで構成されています。

センサーからのアナログ信号は、ADCに組み込まれたアナログマルチプレクサーの入力に供給されます。ADCは、各時間間隔で、信号の1つをアナログ-デジタルコンバーターの入力に切り替えます。

アナログ-デジタルコンバータは、アナログ信号をマイクロプロセッサが動作するデジタルコードに変換するために使用されます。

マイクロプロセッサは、プログラム可能なパラレルインターフェースを介してADCにアクセスします。 ADCの出力から情報を読み取り、RAMメモリセルに入力します。 さらに、MPは、ステーションの出口にある油圧センサーから受信した情報に基づいて、制御アクションを計算します。 この値は、デジタルコードの形式でアクチュエータに送信されます。

RAMは、センサーから受信した情報とマイクロプロセッサ計算の中間結果を一時的に保存するために使用されます。

システムソフトウェアはROM(読み取り専用メモリ)に保存されています。 読み取り操作はマイクロプロセッサによって制御されます。

ROMに格納されているプログラムは、次のシステム操作を提供します。

センサーの順次ポーリング。

アナログ信号のアナログ-デジタル変換の制御。

油圧調整;

表示とアラーム;

電力損失への対応。

システムアルゴリズムの開発

アルゴリズムのブロック図を付録Bに示します。

初期化

この段階で、制御ワードはプログラマブルパラレルインターフェースのRSSに書き込まれます。 PPIDD10はゼロモードで動作します。 ポートは次のように機能します:ポートA-入力、ポートB-出力、ポートC-出力。 PPIDD1はゼロモードで動作します。 ポートは次のように機能します:ポートA-出力、ポートB-出力、ポートC-出力。

ポーリングセンサー

アナログセンサーはADCによってポーリングされます。 ポートAPPI 1を介した個別のセンサーは、マイクロプロセッサーによって問い合わせられます。

RAMに保存

センサーのポーリング後に得られた結果は、一時的な保存のためにランダムアクセスメモリに入力されます。

コントロールアクション

マイクロプロセッサシステムは、受信したデータを分析し、デジタル制御アクションを生成します。

コンセプト開発

デバイスの概略図を付録Dに示します。

アドレスバスは、バッファレジスタとバスドライバを使用して形成されます。 レジスタの選択は、マイクロプロセッサのALE信号によって行われます。 アドレスの上位バイトの負荷容量を増やすには、バスドライバが必要です。

データバスは、DT / RおよびOE信号を適用することによって選択されるバスドライバを使用して形成されます。

システムバスは、信号M / IO、WR、RDの組み合わせを適用することにより、DD10デコーダーを介して形成されます。

表1-制御信号

ROM、RAM、およびその他のデバイスの選択は、デコーダーを介したアドレスバスのラインA13〜A15を使用して行われます。 ROMセルはアドレス0000hから配置されています。

表2-デバイスの選択

|

端末 |

|||

PPI制御ワードのポートまたはレジスタの選択は、アドレスバスのラインA0、A1を介して実行されます。 ディスクリートセンサーは、ポートA PA0-PA7 PPIDD12の入力に供給されます。 ポートBの入力へ-ADC付き。 LEDはポートCの入力に接続されています。

アナログマルチプレクサは、情報を読み取るデバイスを選択するために使用されます。 アナログマルチプレクサはADCに組み込まれています。 ADCのビット幅はデータバスのビット幅と一致し、8ビットです。

抵抗R2〜R4は、4〜20mAの統一電流信号を1〜5Vの電圧に変換するために使用されます。

技術機器の自動化のプロセスは、生産組織全体の大部分を占めています。 それらは、工作機械、機械とメカニズム、ロボット複合体の至る所で使用されています。 新しいテクノロジーは労働生産性を大幅に向上させ、生産のリスクに対する人的要因の影響を減らします。 製品の技術レベルと品質も向上します。 マイクロプロセッサシステム-かつては革新的な技術でした。 しかし、マイクロプロセッサを使用して作成されたデバイスは、別々の論理回路で作成されたデバイスと比較してパフォーマンスが高く、前者の経済的利益があるため、これはすでに一般的です。

開発プロセスの標準化により、この分野の分析と研究が簡素化されます。 また、現在の状態と考えられる結果が明確になります。 今日の組み込みマイクロプロセッサ企業は、フィールドプログラマブルロジック集積回路(FPGA)とコンピュータ支援製造システムを使用して、高速で組織化された設計を行っています。 FPGAの助けを借りて、リアルタイムのデバッグとテストも可能です。 CADを毎年更新することで、明らかな間違いを避けながら、単調で単音節の作業に費やす時間を減らすことができます。 これにより、システムのより高いレベルに抽象化し、困難な問題を解決することができます。

組み込みマイクロプロセッサシステムを開発するプロセスは、連続する設計段階の2つのルートとして表すことができます。 最初のルートは、組み込みマイクロプロセッサシステムのハードウェアの開発です。 2番目のルートはソフトウェア設計です(図1)。

図1.設計段階

ただし、ルートのすべての段階が必要なわけではありません。 開発中のシステムのハードウェアのモデリングは実行されない場合があります。 したがって、モデリング仕様の準備、モデルの生成、機能的および時間的モデリングなど、いくつかのステップを除外できます。 同時に、システムのハードウェアをモデル化すると、発生する可能性のあるエラーを早期に検出して排除できるため、設計プロセス全体の効率が向上することを考慮に入れる必要があります。

マイクロプロセッサシステムの一般的な設計手順は次のとおりです。

- さまざまなシステム要件の形式化。 外部仕様、システムの参照条件(TOR)、ドキュメント内の開発者によるシステムイメージのメモ、システムの機能をリストする必要があります。

- システム要素の構造とアーキテクチャの開発。 ハードウェアとソフトウェア間の相互作用、周辺機器とソフトウェアシェルの機能を決定し、システムを実装するベースとなるマイクロプロセッサソリューションを選択し、時間特性を決定する必要があります。

- システムのハードウェアとソフトウェアの開発と製造。 構造図と回路図を作成し、プロトタイプを作成し、基本的な動作モードの条件でデバッグする必要があります。 ソフトウェア開発は、アルゴリズム、ソースコードの記述、ソースプログラムのオブジェクトプログラムへの変換、ソフトウェアのデバッグ、およびシミュレーションで構成する必要があります。

- 作業条件での一般的なデバッグおよび受け入れテスト。

人的要因により、誤動作や不十分な設計上の決定が可能になります。 デバイスにはハードウェアの欠陥もあります。 たとえば、次の段階的なエラーの原因が考えられます。

ステージ1。要件の論理的な不一致、省略、アルゴリズムの不正確さ。

ステージ2。機能の省略、一部の情報フローの省略、ハードウェアとソフトウェアの相互作用のプロトコルの不一致、技術要件の誤った定義、マイクロプロセッサーソリューションの誤った選択、アルゴリズムの不正確さ。

ステージ3.機器を開発する場合-一部の機能の省略、参照条件の誤った解釈、同期スキームの欠陥、設計ルールの違反。 ソフトウェアを開発するとき-参照条件のいくつかの機能の省略、アルゴリズムの不正確さ、コーディングの不正確さ; プロトタイプの製造において-コンポーネントと周辺機器の誤動作、インストールとアセンブリの誤動作。

リストされているエラーの各原因は、さらに特定して排除する必要のある多数の物理的または主観的な障害につながる可能性があります。 誤動作の検出と特定は、いくつかの理由で複雑です。まず、誤動作のために、いくつかの理由があります。 第二に、さまざまな問題の症状の均一性。 主観的な障害のモデルがないため、このタスクは形式化されていません。 エキスパートシステムの助けを借りて解決することが可能です-既存の問題と実際の経験に基づくそれらの解決策を備えたデータベース。

主観的な障害は、検出、ローカリゼーション、および修正後に発生しなくなるという点で、物理的な障害とは異なります。 ただし、システム仕様の開発段階で主観的な障害が発生する可能性があります。つまり、システムが仕様に対して徹底的にテストされた後でも、システムに主観的な障害が発生する可能性があります。

設計プロセスは反復プロセスです。つまり、ある段階でエラーが完全に排除されない場合、次の段階でエラーが発生する可能性があります。 故障をできるだけ早く発見する必要があります。そのためには、開発の各段階でプロジェクトの正確さを管理する必要があります。 たとえば、プロジェクトの受け入れと納品の最終段階で発見された障害は、仕様の修正につながる可能性があり、その結果、システム全体の設計の開始につながる可能性があります。 参照条件の変更(控えめな表現とシステムに関する情報の欠如による)は、同じ結果につながります。

設計の正確さを制御するための主な方法は、検証、モデリング、およびテストです。

検証により、現在のエラーだけでなく、ブロックを使用して将来のプロジェクトで発生する可能性のある潜在的なエラーも検出できます。 ただし、個別の技術タスクと関連スキルが必要であり、大規模なプロジェクトに適しています。 小規模なプロジェクトでは、オブジェクトの動作のモデリングとテストがより頻繁に使用されます。 このオプションは費用効果が高く、多くのリソースを必要としません。

正確性の制御は、システム抽象化のさまざまなレベルでシミュレーションを実行し、テストを通じてモデルの実装部分の正確性を検証する必要があるため、各設計段階で実現されます。 機能仕様は、モデル化および実験的にテストして、期待される結果を決定できます。 また、専門家のチームが分析することもできます。 機能仕様の承認後、システムの機能テストの開発が開始され、機能仕様に従ってシステムの正しい機能を確立するように設計されています。 この仕様に完全に基づいてテストを開発するのが最も効率的です。これにより、仕様で指定された機能を実行できるシステム実装をテストできるようになります。 この方法は、特定の実装に関連してテストが構築される他の方法と似ていますが、期待値と開発結果をより正確に比較します。

エラーが検出されたら、システムの抽象表現の適切なレベルで適切な場所に修正するために、そのソースをローカライズする必要があります。 エラーの原因を誤って判断したり、システムの抽象表現の別のレベルで調整を行ったりすると、最上位レベルのシステムに関する情報が誤ってしまい、システムの作成および操作中にさらにデバッグするために使用できなくなるという事実につながります。システム。

テストプログラムの開発の反復作業を自動化すると、テストを早期に取得することでビルドとデバッグの期間が短縮され(システム要件が生成されるとすぐに生成できるため)、設計者はすべてのテストプログラムを書き直すことなく仕様を変更できます。 実際には、テストの開発はプロジェクトよりも優先度が低いため、テストプログラムは完了よりもはるかに遅れて表示されます。

したがって、マイクロプロセッサ設計のニュアンスを考慮に入れると、開発中の「落とし穴」を簡単に回避できます。 プログラマブルロジック集積回路(FPGA)を使用すると、まだリリースされていないバッチのデバッグが容易になり、設計のテストとバグの修正が可能になります。 また、コンピューター支援製造(CAD)システムは開発を簡素化し、リソースをより合理的に再割り当てできるようにします。

参考文献:

- SibGUTI [電子リソース] / FPGAでのマイクロプロセッサの設計-アクセスモード:http://ict.sibsutis.ru/sites/csc.sibsutis.ru/files/courses/mps/mp.pdf-無料。 - 頭。 画面から。 - 言語 ロシア (2017年12月22日にアクセス)。

- Zotov V. Embedded Development Kitは、ザイリンクスのFPGAシリーズFPGAに基づく組み込みマイクロプロセッサシステムを設計するためのシステムです。 2004年。第3。

1. 機能している、デザインとアーキテクチャマイクロプロセッサデバイスおよびシステム

1.1。 共通していますマイクロプロセッサ技術に関する情報

基本的な概念と定義マイクロプロセッサ技術

マイクロプロセッサとマイクロコンピュータは、電子産業の大量生産品です。 マイクロプロセッサテクノロジの基本に関する知識は、あらゆるプロファイルのエンジニア、特にシステムエンジニア、設計エンジニア、コンピュータシステム(CS)のプロセスエンジニアに必要です。

マイクロプロセッサ(MP)は、現代の航空機および無線電子機器(REU)、技術制御システム、柔軟な自動化およびその他の業界で広く使用されています。 MPの使用は、労働生産性の向上にプラスの効果をもたらし、さまざまな目的のための機器の品質を向上させます。 技術系でのMPやマイクロコンピューターの使用により、機器の機能が拡張され、動作の信頼性と安定性が向上し、情報処理の質が向上しました。

コンピューティングシステムでMPとマイクロコンピュータを使用する可能性と可能性はまだ完全には明らかにされていません。 MPの生産技術とアーキテクチャは絶えず改善されています。 したがって、最新のシングルチップMPのビット深度は64ビットに達します。 MPとマイクロコンピューターを使用する場合、開発者は、アーキテクチャーの機能と技術的特性を評価できるだけでなく、さまざまなレベルのプログラミング言語に習熟している必要があります。 アセンブリ言語は、システムソフトウェアの作成に広く使用されています。 プログラマーの高い生産性を確保するために、データ処理タスクは高級言語(Cなど)を使用して解決されます。 現代のエンジニア-コンピューター技術の専門家は、MPアーキテクチャとさまざまなレベルの言語での電子デバイスのプログラミングの両方の分野の知識を必要としています。

マイクロプロセッサ技術の基本的な概念は、「マイクロプロセッサ」、「IC」、「IC」、「LSI」、「VLSI」、「LISのマイクロプロセッサセット」、「マイクロプロセッサデバイス」、「マイクロプロセッサシステム」、「マイクロプロセッサ」などの概念です。機器」、「マイクロコンピュータ」(汎用および専用)、「内蔵マイクロプロセッサ」、「パーソナルコンピュータ」、「家庭用パーソナルコンピュータ」、「プロ用パーソナルコンピュータ」、「マイクロコントローラ」など。

また、マイクロプロセッサ技術では、コンピュータ技術に関連する概念、特に「バックボーン」、「バス」、「インターフェース」、「システムインターフェース」、「周辺インターフェース」、「アダプタ」、「プロトコル」、「インターフェース」が使用されます。行」など。

マイクロプロセッサ技術でソフトウェアを研究する場合、コンピュータ技術でソフトウェアを説明する概念と同じ名前の一般的な概念、特に「アルゴリズム」、「プログラム」、「ソフトウェア」などが使用されます。

マイクロプロセッサ技術の主要な基本概念の1つは、「マイクロプロセッサ」です。

マイクロプロセッサ- それ 複雑ソフトウェア制御デバイス、デジタル情報を処理するように設計され、この処理のプロセス制御。1つまたは複数の積分の形式で作成されます。統合度の増加したマイクロ回路(BICまたはSBIと)。

集積回路(IMS)は、信号を変換、処理、および(または)情報を蓄積する特定の機能を実行するマイクロエレクトロニクスデバイスであり、電気的に接続された要素(または要素およびコンポーネント)および(または)結晶の内部パッキング密度が高く、エレクトロニクス製品全体のテスト、配信、および運用要件。

半導体IC-統合されたマイクロ回路。すべての要素と要素間の接続は、半導体の内部と表面で行われます。

デジタルIC-離散関数の法則に従って変化する信号を変換および処理するように設計された集積回路。

統合の程度-ICの複雑さの程度の指標であり、ICに含まれる要素とコンポーネントの数によって特徴付けられます。 統合の程度は、式によって決定されます k=ログ N, どこ k-積分の程度を決定する係数。その値は最大の整数に丸められます。 N-ICの要素とコンポーネントの数。

大規模集積回路(BIと)-バイポーラ技術を使用して製造された500以上の要素、またはMOS技術を使用して製造された1000以上の要素を含む集積回路、特大 積分図式 (SBIと)含む要素の上。

セットするビス-アーキテクチャ、設計、電気的パラメータで互換性があり、マイクロプロセッサ技術の製造での共同使用の可能性を提供するさまざまな機能を実行する一連のLSIタイプ。

マイクロプロセッサキット(IPC)-アーキテクチャ、設計、および電気的パラメータで互換性があり、それらの共同使用の可能性を提供するマイクロプロセッサおよびその他のICのセット。

マイクロプロセッサは、両方の電子デバイスに固有の多数のパラメータ(速度、消費電力、寸法、重量、電力レベルの数、信頼性、コスト、ケースタイプ、温度範囲など)、内部レジスタの数、マイクロプログラムレベル、スタックメモリの種類、ソフトウェアの構成など)。

マイクロプロセッサデバイス( MPU) - 機能的で建設的概略的で建設的な完成品1つまたは複数のマイクロプロセッサを含む複数のマイクロ回路の接続1つまたはを実行するように設計されています複数の機能:受信、 処理、情報の転送、変換、および管理.

MPUは、統一された接続特性(インターフェイス、設計など)を備えており、特定の技術システムの一部として機能します。

マイクロプロセッサシステム( MPS) - それ たくさんの機能デバイス、マイクロプロセッサを搭載しています。

マイクロプロセッサはこのシステムの中核であり、中央制御装置と算術論理データ変換装置の機能を実行します。 すべてのMPSデバイスには標準インターフェースがあり、単一の情報ハイウェイに接続されています。

マイクロプロセッサ技術 - マイクロプロセッサとコンピューティングデバイステクノロジー(VT)と自動化。

これらは、コンピューター技術の最も一般化された概念です。 今日、ほとんどすべてのVTはマイクロプロセッサデバイスに基づいて構築されています。

汎用マイコン - それ 大きいマイクロコンピュータさまざまな処理に適合した運用リソース数値およびテキストデータであり、コンピューティングでの使用を目的としていますセンター。

これは、パーソナルコンピュータのベースとなる最も一般的なクラスのマイクロコンピュータです。

専用コンピューター - それ 特定のを実装するように設計されたコンピューター特定のアルゴリズム:フーリエ変換、相関計算機能とその他

これらは、システムコマンドの数が限られているナロープロファイルコンピューターです。

ビルトイン マイコン(マイクロプロセッサデバイス) - 処理装置データと国内での使用を目的としたコントロール機器、プロセス制御システムまたは制御、コンピュータ周辺機器、オフィス機器など。

これらのコンピューターのほとんどは、家電製品(テレビ、ラジオ、洗濯機など)で使用されています。

パソコン(パソコン) -対話システム個人使用のために、マイクロプロセッサに基づくつまり、小型の外部ストレージデバイスおよびデータ記録デバイス、高水準言語で開発されたプログラミングシステムを使用して、すべてのコンピュータリソースへのアクセスを提供します。

個人用に設計された小型で低コストのユニバーサルマイコンです。 家庭用パソコン家庭情報センターとして機能します。 プロの個人コンピューター専門家の職場で大量の情報を処理するさまざまな操作を自動化するように設計されています。

マイクロコントローラー- 1つまたは複数のチップ上に作成された制御デバイス。その機能は論理的な分析と制御です。

マイクロプロセッサの分類とその主なパラメータ

LSIの数によって、シングルチップ、マルチチップ、およびマルチチップのセクション化されたMPが区別されます。

シングルチップMPプロセッサのすべてのハードウェアを単一のLSIまたはVLSIの形式で実装します。 シングルチップMPは、固定ビット深度と一連のコマンドを備えており、構造的に単一の集積回路(IC)の形式で作成されています。 それによって実行されるすべての操作は、一連のMPコマンドによって決定されます。 シングルチップMPの特徴は、内部情報データと制御信号を送信するための内部高速道路の存在です。 これらのMPの機能は、水晶とパッケージのハードウェアリソースによって制限されますが、水晶の統合度とパッケージピンの数が増えると、MPのパラメータは継続的に改善されます。

V 多くクリスタルMP論理構造は機能的に完全な部分に分割され、別々のLSIとVLSI、または1つのVLSIに別々の水晶として実装されます。

マルチチップパーティションMPマイクロプロセッサセクションのセットで構成されています。

マイクロプロセッサセクション- それ マイクロプロセッサ統合MPの一部を実装し、単純な機能の手段を備えた回路協会完全なMP、MPU、またはマイクロコンピュータを構築するための同じタイプまたは他のマイクロプロセッサセクションを備えています。

セクション化されたMPは、ファームウェアによって制御されます。 セクション化されたMPCには、LSIシリーズK1800、KR1802、KM1804などが含まれます。それらの主な目的は、さまざまな制御コンピュータシステムを実装するための高性能マルチビットMPおよびMPCを作成することです。

IPC BISの基本は、1つのシリーズのICの基本セットです。 これは、固定ビット深度とコマンドのセットを備えたシングルチップMP IC、またはシングルチップMPLSIのセットで構成できます。 MPの機能を拡張するために、基本的なMPC LSIには、RAM、ROM、PROM、インターフェイス集積回路、外部デバイスコントローラなどの他のタイプのLSIが追加されています。

処理される信号の種類に応じて区別されます デジタルと アナログMP。どちらのタイプのMTでも、情報処理はデジタルです。 デジタルMPでは、純粋なデジタル信号が処理されますが、アナログMPでは、アナログ信号を処理するためにアナログ-デジタルデバイス(ADC)とデジタル-アナログコンバーター(DAC)が組み込まれています。 それらでは、入力アナログ信号はADCを介してMPに送信され、デジタル形式で処理され、DACでアナログ形式に変換されて出力されます。

マイクロプロセッサキットの選択

コンピューティングデバイスの設計用およびシステム

特定のコンピューティングデバイスまたはシステムのIPCを選択することは、最も難しい作業です。 これは、IPCとLSIの数が絶えず増加しているためです。

MPCを選択する場合、機器は特定の要件を満たしている必要があります。リアルタイムで動作します。 信頼性の向上。 ノイズ耐性; メンテナンスのしやすさ; 機器の寿命を通して繰り返し解決される固定された一連のタスクの存在。

IPCの選択は、次の3つの主要な基準に従って実行されます。

1)ソフトウェア開発の面では、ビットの深さ、使用可能な汎用レジスタの数、コマンドとアドレス指定方法のセット、スタックの存在と構成を分析する必要があります。

2)システム設計に関しては、MPアーキテクチャのタイプ(セクション化またはシングルチップ)、制御組織のタイプ(マイクロプログラムまたはハードロジック付き)、他のセットからの論理的に結合されたLSIの存在、速度を決定する必要があります。 MPの、中断とメモリへの直接アクセスの可能性、自動化された設計の可用性。

3)MPSハードウェアの開発の観点から、LSIの電気的互換性、電源と消費電力の数、パッケージのサイズとタイプ、ピンの数、動作温度範囲など。

特定のアプリケーション用のRPCの選択は、多くの場合、製造されたテクノロジに基づいて行われます。

質問とタスク

1.実動システムでのMPとマイクロコンピューターの使用を決定する要因は何ですか?

2.シングルチップMPは、マルチチップMP(非セクションおよびセクション)とどのように異なりますか?

3. MP、MPU、MPSを特徴付ける一般的なパラメータは何ですか?

4. MPはどのような理由で特徴付けられますか?

5.最新のMTの主なパラメータに名前を付けます。

6.コンピューティングデバイスおよびシステムを設計するときにマイクロプロセッサセットを選択するための基準は何ですか?

1.2。 一般的な問題組織と機能しているマイクロプロセッサデバイスおよびシステム

マイクロプロセッサデバイスの構造およびシステム

すべてのMPSは、MP、メモリシステム、情報入出力システム、および制御または制御のオブジェクトとインターフェイスするためのシステムで構成されます。

マイクロプロセッサと中央制御デバイスおよび算術論理データ変換用のデバイスの役割を果たします。

メモリーいくつかのレベルで構成されるシステムとして物理的に実装されます。

永続ストレージデバイス(ROM)事前に記録されたデータの長期保存を目的としており、読み出しモードでのみ使用されます。 それらはエネルギーに依存しません。

ランダム・アクセス・メモリ (OZP)プロセッサの速度に近い速度でデータのオンライン書き込みおよび読み取りのモードで動作します。 それらはエネルギーに依存しています。

外部ストレージデバイス(メモリー)大量の情報を保存する機能を実行し、フロッピーおよびハードディスク、コンパクトディスク(レーザー)などにドライブを格納します。

デバイスデータ入力(ID)外部からMPレジスタまたはメモリにデータを転送するように設計されています。 その中には、キーボード、さまざまなコントロールパネル、磁気ディスクやレーザーディスクなどがあります。

データ出力デバイス(UVv) MPレジスタまたはメモリセルから送信されたデータを受け入れるように設計されています。 これらは、ディスプレイ、印刷デバイス、VZU、コントロールパネル、プロッタ(プロッタ)などです。

制御対象または制御対象をMPUまたはMPSとインターフェースさせるには、機器にセンサーとアクチュエーターを含める必要があります。 それらをMPUに接続するには、MPSが使用するかどうか ブロック活用、インターフェイスマッチング機能を実行します。 これらのブロックは、オブジェクトとの通信デバイス(USO)と呼ばれることもあります。

マイクロプロセッサデバイスのインターフェイスおよびシステム

MPSのアーキテクチャ機能は、インターフェイスのタイプに大きく依存します。

統一されたインターフェース は、次のようなルールのセットです。MPSデバイス間の相互作用の統一された原則。

インターフェイスには、デバイス(コネクタ、接続)を接続するためのハードウェア、接続の命名法と特性の仕様、ソフトウェア、インターフェイス信号の性質とそのタイミング図の説明、および信号の電気物理パラメータの説明が含まれます。

インターフェイスの主なタスクは、統合に基づいて、ハードウェア、ソフトウェア、および建設的な手段の互換性を確保することです。これにより、MPSの単一の情報処理プロセスにおけるさまざまな機能要素の自動相互作用の指定された品質が次の段階で事前に決定されます。結果の収集、変換、保存、発行、およびアクションの制御。

MPSアーキテクチャは、主に、システム、マシンツーマシン、およびスモールインターフェイス(周辺機器インターフェイス)の3つのインターフェイスレイヤによって定義されます。

システムインターフェース MPSのメインモジュール(ブロック)を単一のシステムに統合して、プロセッサおよびOZPとの情報を平等に交換できるようにします。

システムインターフェイスは、集中型(PCインターフェイス)、ローカル集中型(Qバス)、ローカル(ユニバス)に分けられます。

マシンツーマシンインターフェースマルチプロセッサシステムとローカルおよび分散システムとネットワークの構築を提供します。

小さなインターフェース周辺機器とROMのグループの動作の物理的原理の違いを考慮に入れてください。 小さなインターフェイスコントローラーは、システムインターフェイスへのアクセスを提供します。 この場合、周辺機器とROMのコントローラは、対応する小さなインターフェイスに移動します。

マイクロプロセッサの管理デバイス(システム)

MPU内の情報信号の時間的調整は、MP制御デバイスからの特別な信号を使用して実行されます。 MPUまたはMPSは、クロック信号の出現と同期して動作します。 MPU(MPS)で実行される最も単純なアクションは次のように呼び出されます。 州。クロック信号の1周期をカバーします- 計時インターバルまたはビート。

一定数のクロック間隔は 機械サイクル。単一のメモリまたはI / Oデバイスへのアクセスには、1マシンサイクルが必要です。 1サイクルで、命令またはデータ、およびアドレスコード(おそらく命令またはデータバイトとアドレスコードバイト)がフェッチされます。

マシンサイクル-チームの一部(チーム全体の場合もあります)。 各マシンサイクルの開始時に、同期信号がMPの同期ピンに表示されます。 これは、ストレージデバイス(メモリ)および(または)入出力デバイス(I / O)に転送され、新しいマシンサイクルの開始について「通知」されます。その結果、これらのアクションのタイミングが実行されます。 MPの動作を備えたデバイスが実現されます。

スキーム1。チーム構造

チームサイクル-メモリからコマンドをフェッチして実行するために必要な時間間隔。 これは、1つ以上のマシンサイクルで構成されます。 それらの数は、原則として、メモリまたはICUの1つへのMTアクセスの数と同じです。 コマンド構造を図1に示します。

制御装置制御と同期の機能を実行します。つまり、MPの状態の変化を必要な順序で制御し、それらをクロックジェネレータの信号と調整します。 これは、MP内のプロセスを制御するように設計された制御有限オートマトンと、外部から信号を受信してシステムを制御する信号を生成する回路で構成されています。

コマンドコードは復号化され、このコマンドの実行に関係するMPモジュールとブロックに作用するバイナリ信号に変換されます。

コマンドサイクルは、フェッチフェーズと実行フェーズの2つのフェーズに分かれています。

サンプリングフェーズ-オートマトンは次のサイクルの開始を設定し、それに応じてプログラムカウンタの番号がアドレスバッファレジスタに転送されます。 そこから、アドレスバスを介して、命令のアドレスコードがメモリに送信され、そこで復号化されます。 メモリセルからの「読み取り」信号の後、コマンドワードが読み取られ、データバスを介してバッファデータレジスタに送信され、そこからコマンドレジスタに転送されてから復号化されます。

実行フェーズ-制御装置は、コマンドの実行に必要な一連の信号を生成します。 この間、カウンタデータは1つインクリメントされます。 これにより、次に実行される命令のアドレスが形成されます。

単語の読み取りまたは書き込みは、アクセス時間と呼ばれる特定の時間間隔で発生します。 メモリへのアクセスとメモリからの準備完了信号の受信に費やされる時間間隔は、準備完了待機サイクルと呼ばれます。 それは機械サイクルの一部を形成します。

MP、メモリ、IUV間の情報交換は、主にプログラム制御交換、割り込みモードでの交換、直接アクセスモードでの交換の3つのモードで実行されます。

ソフトウェア制御の交換。このモードでは、MPは、メモリまたは周辺機器(PU)がI / O操作を実行して、ソフトウェアデータ転送を開始する準備ができているかどうかを判断します。 エアブラスターには、内部状態に関する信号を生成するためのハードウェアが必要です。 MPはこの情報を読み取り、結果の分析に基づいて、デバイスが情報を交換する準備ができていると結論付けます。 将来的には、インターフェースプロトコルに従ってデータが交換されます。

割り込みモード。エアブラストとMP間ですぐにデータを転送する必要がある場合に使用します(予期しない外部条件の発生への対応)。 この場合、MPはメインプログラムの動作を中断し、外部デバイスのサービスのためにプログラムの実行を開始する必要があります。 このモードは割り込みと呼ばれます。 MP割り込みは、MPが割り込み要求に応答できる場合にのみ可能です。

割り込み信号を受信した後、MPは現在の動作を完了し、内部データと制御レジスタのすべての情報をメモリに転送して、割り込みサービスルーチンに進みます。 割り込みに関する情報の交換が終了すると、割り込みの開始時に存在していたMPの状態が復元されます。

割り込みには、単純、ベクトル、優先度の3種類があります。

単純な割り込み一部の入力/出力デバイスにMPサービスが必要であることを通知します。

ベクトル割り込み周辺機器に必要な割り込みの種類(レベル)を認識できるようにします。 ベクトルは、デバイスの特定のアドレスを指定します。

優先割り込み割り込み認識に加えて、割り込みデバイスのサービスの優先順位が決定されるという事実にあります。

ダイレクトモードメモリアクセス。 MPの外部で情報を交換する必要がある場合があります。 これは、データ配列の交換にかかる時間が短縮されたためです。 この場合、MPPまたはMMSのハードウェアには、データ転送を管理するダイレクトメモリアクセスコントローラーが含まれており、MPUをこれらの機能から解放します。

DMAはプロセッサに並列に接続されています。 これらのチャネルの分離は、MPSバスの状態を制御するトライステートロジックを使用して実行されます。 ダイレクトメモリアクセス中のMPは、元の回路をハイインピーダンス状態に転送し、システムから分離されます。これは、情報チャネルを切断するのと似ています。 内部レジスタの状態は、ダイレクトアクセスチャネル要求時と同じように保持されます。

ダイレクトメモリアクセスを実装する方法はいくつかあります。 それらのすべては、プログラム制御の交換モードと比較して最高のデータ交換レートを提供します。 ほとんどの場合、ダイレクトメモリアクセスモードは、MPの停止とMPサイクルの増加(時間の延長)によって実装されます。

停止方法これは、この状態では、データ転送の間、MPがシステムバスから切断されているという事実に基づいています。 停止状態に切り替える前に、MPは現在のコマンドの実行を完了し、タイヤが解放されるまでこの状態で数サイクル残ります。 このダイレクトメモリアクセスのスキームによれば、バスから切断されているMPは割り込みに応答せず、場合によってはMPSに受け入れられない可能性があります。

キャプチャ方法シリアルデータ交換で構成されています。 高速エアブラスターは一言しか交換しません。 それらのサービス要求は、MPが1つのマシンサイクルから別のマシンサイクルに移行する状態にある間、現在の命令の実行を1マシンサイクル遅らせることによって満たされます。 このDMAモードでは、MPは各データワードを転送するために1マシンサイクルだけ一時停止し、その後、制御はMPに戻ります。

アドレス空間。 対処のメカニズムと方法

アドレス空間 MPU(MPS) - 運用アドレスのセット記憶とMPによって実行されるプログラムで使用可能なROM。

MP RAMのアドレス空間のサイズは、MPS全体のパフォーマンスに大きな影響を与える量の1つです。

アドレス空間のサイズ - 価値、これは最大値によって決定されますアドレスサイズであり、最小の単位で表されますアドレス指定されるメモリ要素の数-バイト単位または大容量単位(KB、MB、GB)。

MPUのアドレスが16ビットワードの形式で形成されている場合、アドレス空間は64 KB、20ビットワードは1 MBなどです。MPUのコンポーネント間の情報リンクを簡略化するために、 I / Oプロシージャのプログラミングを容易にし、レジスタアドレスはアドレス空間MPおよびUVVに配置されます。 そのような入出力コマンドはありません。 MPおよびUVVレジスタへのアドレスは、メモリセルへのアクセスと同じです。

2バイトアドレスのワードが形成されると、偶数(下位)アドレスのバイトは下位バイトと呼ばれ、奇数アドレスのバイトは上位アドレスと呼ばれます。

多くの場合、LPAアドレス空間は、アドレスの一般的な範囲を示す図として表されます。 この範囲は、構造モジュール、チップ、さまざまなタイプのメモリ(RAM、ROMなど)の標準サイズ、またはそれらの特定の目的に対応するサブ範囲に分割できます。

MPコマンドシステムでは、アドレスコマンドが重要な位置を占めます。

アドレスコマンド - そのチームそのオペランドの一方または両方はワーキングメモリ内。

このような命令の編成の理由の1つは、命令の長さの制限により、命令の1つのオペランドに完全な物理アドレスを直接書き込むことができないことです。 したがって、特定の値のみがオペランドに配置され、それを使用して命令の実際のアドレスが計算されます。

一般に、アドレス指定メカニズムは、RAMへの最小アクセス回数で情報を効率的に処理するMPU(MPS)の機能によって主に決定されます。 MPU(MPS)では、2語以上のコマンドがよく使用されます。

アドレスワードの長さを制限するために、さまざまなアドレス指定方法が使用されます。これにより、次のことが可能になります。

1)コマンドの長さが短縮されるよりも少ないビットでメモリセルの完全なアドレスを決定します。

2)処理中にアドレスが計算されるメモリーセルにアクセスします。これにより、メモリー拡張デバイスにアクセスできます。

3)命令の位置(現在のアドレス)を基準にしてデータアドレスを計算し、プログラム内のアドレスを変更せずにプログラムを任意のメモリ位置にロードできるようにします。

すべてのアドレッシングモードは、次の2つのグループに分けることができます。

1)コマンドの1つのコード値によって実行アドレスが決定されるモード。

2)コマンドのアドレス部分の内容と1つ以上のレジスタを使用して実行アドレスを形成するコマンド。

最初のグループには、直接、直接レジスタ、間接、間接レジスタ、直接、自動インクリメント、および自動デクリメントのアドレス指定が含まれ、2番目のグループには、基本、相対、スタック、仮想アドレス指定が含まれます。

直接アドレス指定。オペランドは、命令に書き込まれたアドレスのメモリ(レジスタ)からフェッチされます。 ただし、直接アドレスを指定するには、ラージアドレス命令で記述するために多くのビットが必要です。 これを減らすために、一部のマイクロコンピューターは短い直接アドレス指定を使用して、アドレス空間の限られた部分へのアクセスを提供します。 コマンド内のアドレスがシンボリック(リンクで指定)ではなく絶対アドレスである場合、そのような直接アドレス指定は呼び出されます 絶対。

直接レジスタアドレス指定。 V命令コードは、オペランドが配置されているレジスターの名前を格納します。 直接アドレス指定は、メモリ内のプログラムの移動と配列の操作の利便性を確保するために必要なアドレス変更手順を実行できないため、十分な柔軟性がありません。

間接アドレス指定。メモリからのオペランドは、メモリセルを介して間接的に選択されます。 命令コードにはメモリアドレスポインタが含まれています。 このようなアドレス指定で命令を実行する場合、メモリは2回アクセスされます。最初にアドレスが選択され、次にオペランドが選択されます。 したがって、コマンドコードを変更することなく、コマンドコードフィールドが指すメモリ領域に格納されているアドレスを変更することができます。

間接レジスタアドレス指定。速度の点では、間接アドレスはプロセッサの内部レジスタから選択され、追加のメモリサイクルを必要としないため、直接アドレス指定に近づきます。 このアドレス指定方式では、レジスタまたはレジスタペアにオペランドのアドレスが含まれています。 レジスタは、直接アドレス指定のコマンドを使用してロードされます。 間接レジスタアドレッシングモードを使用すると、プログラムの実行中にメモリアドレスを計算できます。これは、データ転送手順や配列要素の表示などで必要になります。

直接アドレス指定。オペランドは命令コードにあります。 この場合のコマンドは、2つまたは3つの単語で構成できます。

自動インクリメントおよび自動デクリメントアドレス指定。実行可能アドレスは、間接レジスタアドレス指定と同じ方法で計算され、レジスタの内容がインクリメントされます。 バイトアドレスのマイクロコンピュータでは、レジスタの内容を1増やして次のバイトを示し、2増やして次のワードのアドレスを示し、オペランドのサイズをオペコードで決定する必要があります。 自動デクリメントモードでは、オペランドアドレスはアドレスレジスタから1または2を引くことによって形成されます。 自動インクリメントアドレス指定との違いは、レジスタの内容が実行アドレスとして使用される前に減算が行われることです。 自動インクリメントモードと自動デクリメントモードの組み合わせにより、任意のレジスタをスタックポインタとして効果的に使用できます。 このアドレス指定は、ループを編成するときや文字列変数を使用する操作でも使用されます。

ベースアドレス。絶対アドレスを持つ命令を含むプログラムは、アドレスを変更せずにメモリ内で移動することはできません。 基本アドレス指定を使用してメモリ内のプログラムを確実に移動できます。これを使用すると、ベースレジスタの内容(正または負のオフセットと命令コードにあるアドレス)を加算してオペランドのアドレスを計算できます。

相対アドレス指定。実行可能アドレスは、命令のアドレスフィールドにベースアドレスを追加することによって形成されます。 ベースアドレスとして、プログラムカウンターの内容が使用されます。 相対アドレス指定を使用すると、プログラムカウンターの内容に対して常にオフセットを指定するため、メモリ内で独立して移動するプログラムを構築できます。 オフセットは、いずれかの方向へのジャンプを提供する2の補数の符号付き整数として解釈されます。

スタックアドレス指定。自動インクリメントまたは自動デクリメント(自動インクリメントまたは自動デクリメント)を使用した間接レジスタアドレス指定。オペランドアドレスポインタを使用したレジスタが暗黙的に指定されます(オペランドの位置と結果が固定されている命令があります-暗黙のアドレス指定)。 暗黙的に定義されたレジスタ(スタックポインタ)の内容が指すメモリ位置が呼び出されます サミット スタック。スタックアドレス指定は、と呼ばれるメモリへの特別なアクセスを提供します スタック、これは「後入れ先出し」の原則に基づいています。 スタックにアクセスするには、スタックとの間で情報を書き込む命令が使用されます。 スタックに情報を書き込む命令がスタックポインタの内容をデクリメントし、スタックから情報を削除する命令がインクリメントする場合、スタックは減少するように機能し、そうでない場合は増加するように機能すると言います。

仮想アドレス指定。適用された問題を解決している間、メモリの各ユーザー(オペレーティングシステムまたは人)は仮想アドレスを操作します。これにより、システムの実際のRAMの容量は限られていますが、容量が無制限のメモリのように見えます。 錯覚は、システムのメインメモリ(OZP)と外部メモリ間のメモリページの動的な再配布に基づく仮想アドレス指定メカニズムによって作成されます。

オペレーティングシステムは、ユーザーごとに、仮想ページと物理ページの間の対応のテーブルを作成します。 メインメモリにない物理ページにアクセスすると、外部メモリから削除されてメインページにロードされ、不要なページは外部メモリに「非表示」になります。 仮想メモリ、または単にシステムメモリは、機能機能に従って情報が格納されるセグメントに分割できます。 たとえば、1つのセグメント(コマンド)、2番目のセグメント(データ)、3番目のセグメント(スタックのセクション)。 または、書き込みが禁止されている1つのセグメント(オペレーティングシステムカーネル)と、書き込みと読み取りが許可されている2番目のセグメント(ユーザープログラム)。 したがって、セグメンテーションメカニズムの助けを借りて、メモリ保護の問題が解決されます。

セグメンテーションはK1810VM86MPに実装され、仮想アドレス指定はIAPX286 MP(Intel)および68010(Motorola)に実装されました。

コマンドシステム。一般に、コマンドは、機械語での命令の形式での実行デバイスの操作における単一のステップとして理解されます。 このコマンドは、実行する操作とその属性を定義します。特定の作業サイクルで実行する操作のタイプ。 操作に関係する1つまたは2つのオペランドのアドレス。 操作の結果の場所。 次のコマンドの場所。 MPの容量が小さいため、このような情報を1つのマシンワードで示すことは困難であり、場合によっては不可能です。 したがって、コマンドは複数のマシンワードで構成できます。

一般に、次のタイプのコマンドが区別されます。

1)転送-単方向(レジスタレジスタ、メモリレジスタ、レジスタメモリ、メモリメモリ)、交換(レジスタレジスタ、メモリレジスタ、メモリメモリ)、入力/出力コマンド。

2)算術;

3)論理的;

4)ビットの処理。

5)計算の順序を変更するもの-ジャンプ(無条件、条件付き)、サブルーチンの呼び出し、サブルーチンからの戻り、ソフトウェア割り込み。

自己診断のための質問

1.MPおよびMPSの一般化された構造を説明します。

2. MPUおよびMPSインターフェイスはどのような理由で分類されますか?

3.サンプリングフェーズ、実行フェーズでコマンド(命令)を処理する場合、MPはどのような機能を実行しますか?

4. MPとストレージデバイス間の情報交換は、中断モードまたはメモリへの直接アクセスモードでどのような状況で実行されますか?

5.アドレス空間のサイズはMPのどのパラメータに依存しますか?

6.付録1を使用して、直接、間接、即時、ベース、相対、自動インクリメント、スタック、および仮想アドレス指定を使用したアドレスコマンドの例を示します。

7.コマンドコードはMPコマンドシステムでどのような情報を伝達しますか?

1.3。 プロセスの形式化設計マイクロプロセッサデバイスおよびシステム

デザインの側面とレベル

MPUとMPSを設計するとき、多くの場合、それらは使用します ブロック階層的アプローチ、設計中のシステムは、階層レベルに分割されています。 最高レベルでは、最も詳細でないビューが使用され、一般的な機能と設計中のシステムの機能のみが表示されます。 次のレベルでは、詳細レベルが上がります。 この場合、MPSは個々のブロックのセットと見なされます。 各レベルで、特定の複雑さのタスクが定式化および解決され、このレベルで使用可能な設計ツールを使用して実装されます。 ブロックの割り当ては、個々のブロックのドキュメントが1人の設計者に理解できるようにする必要があります。

したがって、ブロック階層アプローチにより、大規模なMPSを設計する複雑なタスクを小規模なタスクのグループに分散でき、グループ内でさまざまなタスクを並行して解決できます。

ESKDに従って、デバイスとシステムを設計する際に、構造図、機能図、および概略図が使用されます。

シミュレートされた設計スキームでは、条件付きで水平レベルと垂直レベルを区別することができます(表1)。 垂直レベルはアスペクトと呼ばれます。 MPUとMPSの設計には、機能、アルゴリズム、設計、技術などの側面があります。

機能面 3つの水平レベル(2番目、3番目、4番目)で構成されています:システム(構造)、機能論理、回路コンポーネント。 システムレベルでは、MPUまたはMPSのブロック図が、機能論理レベルで設計されます。MPUまたはMPSの一部であるすべてのデバイスの機能図と概略図です。

回路コンポーネントレベルの回路サブレベルでは、集積回路またはLSIフラグメント(VLSI)の回路図が設計されます。 この場合の要素は、電子回路のコンポーネントです。抵抗、コンデンサ、ダイオード、トランジスタなどです。コンポーネントのサブレベルでは、半導体結晶の要素セクションで構成される個々のICコンポーネントが開発されます。

アルゴリズム的側面また、3つの水平レベル(1番目、2番目、3番目)が含まれています。MPUまたはMPSの動作スキームの開発レベル、アーキテクチャレベル、およびファームウェアレベルです。 第1レベルでは、MPUまたはMPSの機能のためのスキームを開発し、MPSのマイクロプロセッサ部分によって解決されるタスクを決定し、ソフトウェアシステムを計画し、アルゴリズムのブロック図を開発します。 ソフトウェアモジュールのさらなる開発。

第2(アーキテクチャ)レベルの主なタスクは、MPSのマイクロプロセッサ部分のアーキテクチャの選択です。 これは、システムレベルのタスクの1つと見なされる場合があります。つまり、アーキテクチャレベルとシステムレベルが組み合わされて、機能設計の1つの側面になります。

表1。水平および垂直設計レベル

水平レベル

アスペクト(垂直レベル)

機能的

アルゴリズム

設計

技術的

LPA(MPS)の機能に関する法律の開発。 アルゴリズム設計; モジュールプログラミング

全身(構造的)

建築(機械)

ライザー、パネル

技術プロセスの概略図の開発

機能的-論理的

マイクロソフトウェア

TEZ、モジュラー

技術プロセスルートの開発

Circuit-technical-component-ny

ICクリスタル

技術運用の設計

3番目の(マイクロプログラム)レベルは、MPUマイクロプロセッサまたはハードウェアのMPSで実行される操作と手順のマイクロプログラムを設計することを目的としています。

デザイン面ライザー、パネル、TEZ_v、モジュール、およびクリスタル(chip_v)ІС(2番目、3番目、4番目が等しい)を設計する水平階層レベルが含まれています。

技術的側面 2番目、3番目、4番目の3つの水平レベルで構成されます。 第2レベルでは、MPUまたはMPSを製造するための技術プロセスのスキームが開発されます。つまり、MPU(MPS)を製造するための段階の構成と順序が決定されます。 第3レベルでは、MPU(MPS)の製造のための技術プロセスのルートが開発されます。つまり、製品の製造のための操作の構成と順序を決定し、技術機器のタイプとグループを選択します。 第4レベルでは、MPU(MPS)コンポーネントを製造するための技術的操作が設計されます。

設計レベルの主なタスク

システムとアーキテクチャ設計レベル:

1)LPA(MPS)の組織化の原則の決定。

2)ブロック図の作成、つまり、デバイスまたはシステムの構成の定義と、機器の機能プロセスにおけるそのコンポーネントの相互作用の方法。

3)LSI(VLSI)のマイクロプロセッサ(マイクロプロセッサ)セットの選択。

4)デバイスまたはシステムのパラメーターの要件の決定、および個々のMPSデバイスの開発のための技術タスク(TOR)の形成。

個々のMPSデバイスを開発するためのToRには、次のものが含まれます。各デバイスによって実行されるすべての機能の列挙。 デバイスの動作条件。 入力パラメータと出力パラメータの要件。 機器の他のデバイスと交換される情報の内容と形式に関するデータ。 デバイスを作成するための要素ベース。

機能-論理およびファームウェア設計レベル:

1)各デバイスの機能の詳細。

2)プログラムで実行される関数のアルゴリズムによる実装、および受け入れられているアルゴリズム言語の1つでのアルゴリズムの提示。

3)LPA(MPS)の組織化とその概念の開発のための原則の選択。

4)各コマンドまたはマイクロコマンドのセットの基礎として機能するマイクロプログラムの開発とそれらの実行の順序。

5)MPSの一部であるデジタルデバイスの機能図と回路図の統合。

6)MPPまたはMPSの監視および診断テストの統合。

7)回路設計レベルのTORの定式化。

複雑なMPPの主な設計基準とMPS:

1)デザイン品質;

2)設計コスト。

3)開発条件;

4)雇用されたスペシャリスト-開発者の数。

設計プロセスの形式化の可能性とその反復性に応じて、MPPまたはMPSのコンピューター支援設計の選択が優先されます。 今日、MPPとMPSは非常に複雑であるため、マイクロプロセッサ部品の完全な開発は、コンピュータ支援設計手法を使用せずに一般的に不可能です。

質問。 仕事

1.MPPおよびMPSの設計に対するブロック階層的アプローチの本質を説明します。

2.シミュレートされたMPP設計スキームでアスペクトは何を表していますか?

3. MPPがTKとして設計されている水平レベルはどれですか。また、これに対応する側面は何ですか。

4.MPPを設計するシステムレベルの主なタスクに名前を付けます。

5. MPP設計のアーキテクチャレベルの特徴は何ですか?

6. MPPおよびMPSを設計する機能的論理レベルの本質は何ですか?

7. MPPのマイクロプログラムレベルで解決される主なタスクは何ですか?

1.4。 建築マイクロプロセッサデバイスとシステム

アーキテクチャと原則の本質

マイクロプロセッサデバイスおよびシステムの開発

建築の本質MPUおよびMPS。

マイクロプロセッサアーキテクチャ 表現に使用される構成電子部品の機能に反映データ、機械操作、アルゴリズムと計算プロセスの説明.

このアーキテクチャは、コンピュータテクノロジのハードウェア、ファームウェア、およびソフトウェアを組み合わせており、特定のMPSを作成するときに、ソフトウェアおよび追加のハードウェアでユーザーが実装する必要があるものを明確に識別できるようにします。

それ以外の場合、MPのアーキテクチャは、設計されたMPUまたはMPSに割り当てられた機能のハードウェアまたはソフトウェアの実装に関するMPの機能により、その論理的な構成になります。 MPの構造、表現方法とデータ形式、コマンドのセット、制御ワードの形式、ユーザーがアクセスできる構造のすべての要素にアクセスする方法、および外部信号に対するMPの応答が表示されます。

MPアーキテクチャは、ユーザーの観点から、そのプロパティと特性のセットと見なすことができます。 開発者とユーザープログラマーが使用するプロパティに関して、LPUまたはMSMのハードウェア、ソフトウェア、およびファームウェアの組み合わせを最適に組み合わせるための方法論について説明します。

開発時 建築MPU、MPの場合と同様に、データとコマンドの形式、コマンドシステムとアドレス指定方法が決定され、アドレス指定のタイプ、インターフェイスの要件が実証されます。 アーキテクチャを正しく選択することで、MPUが機能するためのアルゴリズムを実装する計算プロセスを最適化することができます。

建築 マイコン -機能ユニット、メインコンピュータモジュール、データ構造に関するマイクロコンピュータの抽象的な概念。 アーキテクチャは、ハードウェアの機能、コマンドの実行時間、プログラムの実装における並列度、およびその他の同様の特性を具体的に定義していません。 これは、マイクロコンピューター構造の側面、特に、コマンドのシステム、アドレッシングモード、データ形式、ユーザーが使用できるレジスターのセットを表示します。 「アーキテクチャ」という用語は、マイクロコンピュータが提供する機能を説明するために使用され、「組織」という用語は、これらの機能がどのように実装されるかを定義します。

アーキテクチャの説明 はマイクロコンピュータモデルであり、その理解はプログラマーだけでなく重要です。 これは、新しいマイクロコンピューターの潜在的な開発者の初期ベースとして使用できます。この場合、開発者は、特定の論理スキームを表すアーキテクチャの要素、必要な相互接続されたコンポーネントのセットを変換します。

すべてのマイクロコンピュータには、独自の内部マイクロアーキテクチャを備えた機能ブロックが含まれています。1)プロセッサ、算術論理演算装置と制御装置で構成されています。 2)メモリは、ストレージ要素(セル)と制御ユニットのセットです。 3)情報入力および出力デバイスも、機械的および電子的モジュールを組み込んだ複雑なデバイスです。 これらの機能ブロックは、バスシステムを使用して結合されます。データバス。マイクロコンピュータユニット間で情報が交換されます。 ソフトウェア制御デバイスにアドレスを転送するために使用されるアドレスバスと、制御ワードを転送するための制御バス。

意味 コンピュータアーキテクチャ、ユニバーサルマイクロコンピュータとして、一般的なマイクロコンピュータアーキテクチャの定義と意味に違いはありません。

コンピュータアーキテクチャ , プログラマーの観点からは、複雑なハードウェアとソフトウェアのセットとしてのコンピューターシステムの抽象的な表現(または定義)。 本質的に、アーキテクチャはコンピュータの機能的(論理的)構成に関する情報です。

建築 MPS -個々のレベルでシステムによって実装される機能の定義、およびこれらのレベル間の境界の正確な定義。 これは、MPSの編成の原則と、そのコンポーネント、特にプロセッサ、メモリなどの機能を定義します。MPSのアーキテクチャは、論理構造とモジュールの設計機能およびそれらの製造技術を反映していません。

開発の原則MPUおよびMPS

当初から、マイクロコンピューターの設計と開発では、モジュール性、バックボーン、マイクロプログラマビリティ、構造の規則性という基本原則が主に使用されていました。

原理 モジュール式の組織 モジュールのセットに基づいてマイクロコンピューターとMPSの構築を提供します。

モジュール -建設的、機能的、そしてe電気的に仕上げた端末、これにより、単独で、または他の製品と組み合わせて使用できますモジュール計算または制御の問題を解決する与えられたクラス。

区別 機能的と 建設的モジュール。 モジュール式のアプローチにより、より高いレベルの要素を標準化することが可能になり、MPUおよびMPSの設計コストが削減され、能力開発とシステムの再構成が簡素化されます。

モジュールとその要素の間の接続は、主に次の2つの原則に従って実行されます。 任意の原則接続、これは「eachwitheach」ルールを実装します。b) 原理注文した接続- トランク、接続数を最小限に抑えることができます。 これらは、入力バスと出力バスを接続する高速道路を使用して、さまざまなレベルの機能モジュールと建設モジュールの間で情報交換を提供します。

ほとんどのマイクロコンピューターとMPSには、プログラム制御のマルチレベル構成があります。

原理 ファームウェア制御 多機能マイクロプロセッサモジュールの編成に最大の柔軟性を提供し、マイクロコマンドの特定の組み合わせを通じて、マイクロコンピュータの問題の方向付けを実行することを可能にします。 この原理により、MPSでマクロ演算を使用し、サブルーチンを使用する場合よりも効率的にコマンドやプログラムを実行することができます。

ファームウェア制御は以下を提供します:

ファームウェアを変更できるため、デバイスの柔軟性が向上します。

メモリなどのマトリックス構造を広く使用することにより、デバイスの構造の規則性を高めます。

分散制御と分散メモリの問題に対する並列ソリューションを提供します。

メモリチップを使用してデバイスの信頼性を高め、

マイクロプログラム制御ユニットの制御が記憶装置の内容物の制御に限定されるので、装置の機能の制御を単純化する。

規則性の原則 構造の要素の再現性とそれらの間の関係を事前に決定します。

システムの規則性は、原則として、組織のさまざまなレベルで考慮されます。 MPPおよびMPSの構造の規則性を高める主な方法は次のとおりです。

1)メモリデバイスの広範な使用。

2)特定のマイクロオペレーションをレジスタに割り当てることを拒否する。

3)レジスタ構造の使用。

4)メモリーセルの形での汎用レジスターおよびその他のレジスターの作成。

5)情報交換の主な方法の適用。

7)マイクロプログラム制御の原理を使用する。

8)並列MPSの開発。

マイクロプロセッサデバイスおよびシステムのアーキテクチャの分類

MPUおよびMPSアーキテクチャにはいくつかの分類があり、これらは一般化されたコンピュータアーキテクチャの説明とほぼ一致しています。

分類M.フライナ。これは成功した分類の1つであり、コンピューター間のアーキテクチャの違いを示しています。 コンピューターのアーキテクチャー機能は、コマンド(命令)のフローとデータ・フローの観点から説明されています。 このアプローチにより、コンピュータアーキテクチャを特定のクラスの1つに割り当てることができます(表2、スキーム2)。

表2フリンのコンピュータアーキテクチャの分類

コマンドフロー

単一のデータストリーム

マルチデータストリーム(MD)

シングル(OK)

OKOD(SISD)(シングルプロセッサコンピューター)

SIMD(並列または連想プロセッサを搭載したコンピュータ)

複数(MK)

MKOD(MISD)(コンベアメインコンピュータ)

MKMD(MIMD)(マルチプロセッサまたはマルチマシンコンプレックス)

分類は、マシンの構造ではなく、コンピューター内でそのマシン命令がデータとどのように相互作用するかという観点から実行されます。 それにもかかわらず、フリンの分類は非常に一般的です。つまり、マルチプロセッサを除くすべての並列コンピュータを同じクラスに参照し、パイプライン化されたコンピュータとMPマトリックスの違いを示すものではありません。

アーキテクチャの他の分類も使用されます。特に、F。Sharの分類学、R。HockneyおよびC. Jeshopeの構造分類学は、特別な構造表記を使用します。

構造分類学R。ホックニーとC.ジェスショップ. 最初のレベルでは、すべてのコンピューティングシステムは、多重度(数量)の原則に従って、シングルコンピューターシステムとマルチコンピューターシステムに分けられます。 次に、1台のコンピューターを備えたコンピューティングシステムは、1台のコンベヤーMPと多数のMPを備えたコンピューターに分割されます。

それらの最初のものは従来のシリアルコンピューターであり、2番目はパイプライン化された非パイプライン化されたマイクロプロセッサーマトリックスに分割された並列コンピューターのクラスを形成します。

スキーム2。フリンのコンピュータアーキテクチャの分類の図

並列処理を備えた最初の非パイプラインコンピューターの例としては、いくつかのスカラープロセッサーに基づいて構築されたCDC-6600コンピューターがあります。

パイプラインコンピューターは、CDC-7800、FPC AP-120Bコンピューターなどのスカラー命令のみを実行するコンピューターと、ベクトル命令を実行するコンピューターに分けられます。 ベクトル命令を使用するコンピューターは、CRAY-1などの特殊なパイプラインを備えたコンピューターと、ユニバーサルパイプラインを備えたコンピューター(CYBER 205コンピューター)に分割されます。

マシンクラスのコンピューター プロセッサのマトリックスを使用これらは、マトリックス内のプロセッサの接続性、容量などに応じて分類されます。このタイプの最初のマシンは、ILLIAC-IV、BSP、STA-RAN、ICL DAP、OMENなどでした。

目的により、コンピューターは2つの主要なグループに分けられます。 ユニバーサル と 専門 .

建築フォンノイマン

ユニバーサル コンピュータには、従来の「フォンノイマン」アーキテクチャ(またはスカラーアーキテクチャ)があります。

プログラム制御のコンピューターを構築するための基本原則。

1946年、有名なアメリカの数学者J. von Neumannは、プログラム制御のコンピューターを構築するための基本原則を初めて策定しました。

1)プログラム制御の原則は、コンピュータが特定のプログラムに従ってソースデータを自動的に変換できることです。

2)条件付き遷移の原則は、プログラムに柔軟性と多様性を提供し、中間計算または初期データの結果に応じて、プログラムの特定のセクションへの遷移を実行する問題を解決するプロセスの機会を提供します。

3)プログラムの永続性(セキュリティ)の原則は、プログラムがコンピュータのストレージデバイスに配置されることです。

4)メモリ要素へのランダムアクセスの原則。

5)2進数システムを使用する原則。

6)マルチレベル(階層)メモリの原理。

これらの原則は、最新のコンピューターにも関連していますが、新しい世代やコンピューターファミリーの作成により、それらは補完され、洗練されました。

コンピューターでは、 第三世代、さらに、次の原則が適用されます。

- マルチプログラミング-RAMに保存されている、同じまたは異なる、独立したプログラムの異なるコマンドの共同実行。

- 情報とソフトウェアの互換性-ファミリのさまざまなモデルで既存のプログラムを実行できるようにします。

高い 技術標準化のレベル-すべてのマシンに共通の外部デバイスおよびその他のデバイスの命名法。

機会 多段階作業の編成コンピュータの作成と改善について。

第4世代のマシン以下の原則に基づいて構築されています。

- マルチプロセッシング-共有メモリを使用する場合の複数のプロセッサの切り替え。

組織 仮想メモリ-ほぼ無制限のRAMアドレス空間を提供します。

幅 BIの使用CおよびVLSIマクロモジュラー構造は、大規模な標準化されたブロック(マクロモジュール)から機能的に柔軟なコンピューティングシステムを構築するというアイデアに基づいています。

内部の使用 高水準言語.

第5世代のマシン異なる:

プロセッサの知的レベルの大幅な向上。

グラフィック、画像、ドキュメント、プログラミング言語の入出力機能のさらなる開発。

自然言語を使用した情報のインタラクティブな処理の可能性。

自己学習、連想構造、結論を引き出す能力。

プログラムを形成する過程のプログラミング言語は、人と機械の間に自然なインターフェースを実装することができます。 超高級言語は以下を提供します:

必要な情報を選択するためのデータベースおよび、なじみのないタスクを解決するために必要な新しいアイデアを取得するための知識ベースへのアクセスのさまざまなレベルでのコンピューティングシステムとのユーザーインタラクションの高レベルのインテリジェンス。

従来のコンピュータアーキテクチャに向けられた既存のソフトウェア資金の使用。

スペシャライズド コンピューターは、解決する際のパフォーマンスを大幅に向上させるように設計されています 特定のタイプタスク。 これは、最初は並列コンピューティングを使用して実現されました。 時間の経過とともに、さまざまな機能の並列実行または算術デバイス、特にプロセッサマトリックスの複製に基づいたマシンが登場しました。

並列アーキテクチャ

並列処理は2つの方向に発展しました:

1)プロセッサの速度とRAMへのアクセス速度の差を減らすことにより、コンピュータの構造を改善します。

2)特定のトポロジーに従って組み合わされた同じタイプのコンピューターデバイスの繰り返し。

並列処理は、いくつかの階層レベルで適用されました。特に、次のとおりです。

1)タスクのレベル-コンピューターで実行されるタスク間、またはタスクのフェーズ間。

2)プログラムレベル-プログラムの各部分の間(たとえば、サイクルの境界内)。

3)コマンドレベル-コマンド実行のフェーズ間(プロセッサ命令)。

4)算術およびビットレベル-算術ユニットの論理回路内のベクトル演算の要素間。

基本的 方法並列処理の導入コンピュータアーキテクチャは、次のグループに分けることができます。

- 機能処理-さまざまな機能、特に論理演算、加算、乗算などを実行する機能を複数のデバイスに提供します。

- パイプライン処理-プロセッサデバイスの効率を高めるためのコンベヤ原理の使用。

- マトリックス処理-共通の制御システムを備えた同一のプロセッサ要素のマトリックスの使用。すべての要素が同じ操作を実行しますが、データは異なります。

- マルチプロセッシング-複数のプロセッサによって実行され、各プロセッサは独自の命令を実行し、それらはすべて共通のRAMを介して相互作用します。

信号とm単一のマイクロプロセッサ

シグナルマトリックスプロセッサ - プロセッサ、に基づいています経営理念ストリーム自体によってデータ。

命令は、オペランドが使用可能になるとすぐに実行を開始します。 この場合、隣接するプロセッサからのデータの到着は状態変化として解釈され、特定のアクションを開始します。

信号プロセッサは信号伝搬のように機能します。 それらは分散型グローバル非同期行列コンピューティングシステムです。

メディアシステム - プロセッサネットワーク、リズミカルに演奏するシステムによる計算とデータ送信。

各プロセッサは、常にデータを定期的に送り出し、特定の短い計算を実行して、データストリームがネットワークに定期的に保存されるようにします。 これらの各プロセッサは、1つのクラスのタスクのみに焦点を合わせているため、専用コンピュータのクラスに属しています。

ハードウェアレベルでは、これらのコンピューターにはグローバル同期があり、クロック同期、消費電力の増加、信頼性の低下などの問題の発生を事前に決定します。

汎用ストリーミングマルチプロセッサシステムの場合、共有メモリの使用とプロセッサの相互作用に関連する競合は重大です。 これらの問題は、ストリームシステムをモジュラーシステムとローカルシステム(シグナルマトリックスプロセッサに実装されている)に置き換えることで解決されました。

多くの専用コンピュータは 「ハーバードアーキテクチャ」 , その本質はそれです 命令メモリスペースメモリ空間から分離データ命令とデータを同時にフェッチするため。

RISCコンピュータアーキテクチャ

命令/コマンドのセットが削減されたコンピューター( RISC - 縮小命令セットコンピュータ).

コンピュータの基本的な特性と RISC-建築:

1)少数のフォーマットタイプでの固定長コマンドの使用。

2)規則性。これにより、コマンドが単純であるため、同じハードウェアデバイスを使用してほぼすべてのコマンドを実行できます。

3)1つのマシンサイクル(サイクル)でほとんどのコマンドを実行します。

4)レジスタに焦点を当てる-ロードおよび書き込みコマンドを除いて、すべてのデータ操作はレジスタで実行されます。ロードおよび書き込みコマンドの実装はメモリアクセスに関連付けられています。

利点 RISC-建築:

1)ハードウェア実装の同等の単純さ。

2)コマンドの高速復号化。

3)サイクルの持続時間が短く、したがってコマンドの実行が速い。

4)効率的なコマンドパイプラインを作成する機能。

欠陥 RISC-建築:

1)オペランドとRAMセルの交換レートが比較的低い。

2)追加のソフトウェア要件。

最新のマトリックスおよび並列コンピューターのパフォーマンスは非常に高く、浮動小数点演算を実行すると、64ビットオペランドで1秒あたり数十億の演算に達します。 適用された問題を解決すると、それらのパフォーマンスは大幅に低下し、最新のユニバーサルコンピューターのパフォーマンスに近づきます。

最新のパイプラインおよびマトリックスMPSの中で、CrayMPなどのスーパーコンピューターについて言及する必要があります。

質問。 仕事

1. MPU(マイクロコンピューター)アーキテクチャーは何を表示し、MPアーキテクチャーとどのように異なりますか?

2. MPU、マイクロコンピューター、およびMPSの開発で使用される、モジュール性、バックボーン、マイクロプログラマビリティ、および構造の規則性の原則の本質を説明します。

3.コンピュータアーキテクチャはどのような基準で分類されますか?

4.フォンノイマンのコンピュータアーキテクチャの本質は何ですか?

5.コンピュータハーバードアーキテクチャの本質は何ですか?

6.コンピュータアーキテクチャに並列処理を導入する方法をリストします。

7.本質を説明する マルチプログラミングコンピューター。

8. MPメディアネットワークとシグナルマトリックスMPの動作原理は何ですか、それらの違いは何ですか?

9.コンピューターのRISCアーキテクチャーの本質は何ですか。以前に検討されたアーキテクチャーと比較して、どのような長所と短所がありますか。

文学。

1. virobnicheskihシステムのマイクロプロセッサとmicroEOM:Posіbnik.-- K。:Vidavnichiy center "Akademiya"、2002.-368p。 (母校)。

2.Korneevコンピューティングシステム。-M.: "Knowledge"、199p。

3.、Kiselevマイクロプロセッサ。-M.:「知識」、199p。

VTツールの要素ベースの質的および量的変化は

それらの設計の確立された原則を変更する(たとえば、剛体

構造、順次中央制御、ライン編成

メモリとコンピュータの構造を機能に適応させることができない

問題が解決されています)。

コンピュータシステムを編成するという古典的なフォンノイマンの原則は、MPSの問題指向、情報の並列およびパイプライン処理、表形式のデータ処理方法の使用、MPS構造の規則性と均一性の原則の概念に置き換えられました。 リアルになる

適応調整可能なシステムを作成するというアイデアの可能性、および

ソフトウェア機能のハードウェア実装。 したがって、現在

受け取ったMPSに基づくコンピューティングシステムの設計の時間

いわゆる「3M」原理の適用:モジュール性、トランク、

マイクロプログラマビリティ。

モジュール編成の原則コンピュテーションと

モジュールのセットに基づいてMPSを制御します:構造的、機能的、および

独立してできる電気的に完全なコンピューティングデバイス

または、このクラスの問題を解決するために他のモジュールと組み合わせて使用します。 基本単位

マイクロコンピュータとシステムの設計におけるアプローチは、次のことを可能にします(

普遍的で特殊なモジュール)家族の作成を確実にする

(行)MPSの、機能と特性が異なる、

かなりの範囲のアプリケーションをカバーし、削減に役立ちます

設計コストだけでなく、容量の拡張を簡素化し、

システムの再構成は、コンピューティングの時代遅れを押し戻します

情報交換のバックボーン方式組織とは異なります

任意の接続(「それぞれ」の原則による)により、合理化と

MPS内のリンクの数を最小限に抑えるため。 それは間の情報交換を提供します

を使用したさまざまなレベルの機能的で建設的なモジュール

入力バスと出力バスを組み合わせた高速道路。 1つ、2つ、

3回線および複数回線の通信。 関係に注意する必要があります

実装中に現れる回路および構造ソリューション

特別な双方向バッファを作成する形でのこの交換方法

3つの安定した状態と一時的な使用を伴うカスケード

交換チャネルの多重化。

ファームウェア制御整理に最大の柔軟性を提供します

多機能モジュールと問題の方向付けを可能にします

MPS、およびそれらでマクロ操作を使用します。これは、MPSを使用するよりも効率的です。

標準ルーチン。 さらに、形式で制御された単語の送信

暗号化されたコードシーケンスは最小化条件に対応します

VLSIピンの数を増やし、モジュール内の相互接続の数を減らします。

上記のMPS設計の主な機能に加えて、次のようにする必要があります。

規則性の原則に注意してください。これは規則性を意味します

MPS構造の要素とそれらの間のリンクの再現性。 これの適用

原理により、積分密度を上げ、結合長を短くすることができます

チップ上で、レイアウトと回路設計の時間を短縮します

LSIとVLSIの設計、交差点の数と機能の種類を減らす

および構造要素。

MPS(システムステージ)のアーキテクチャを開発する場合、以下を解決する必要があります。

システムの機能的振る舞いの概念的構造の説明を

その構築と組織化におけるユーザーの利益を考慮に入れる立場

その中のコンピューティングプロセス。

ソフトウェアの構築の構造、命名法、および機能を決定し、

ファームウェア;

データフローと制御の内部組織の特徴を説明する

情報;

物理的な機能構造と機能の分析を実施します

ソフトウェアバランスの観点からのシステムデバイスの実装、

マイクロプログラムとハードウェア。

MPS設計の主な段階を図1に示します。 3.1。

初期の設計段階では、MPSは次のいずれかで記述できます。

次の概念レベル:「ブラックボックス」、構造、プログラム、

論理、スキーマ。

「ブラックボックス」レベルでは、MPSは外部仕様によって記述されます。

外部特性がリストされています。

米。 3.1。 MPS設計の段階

構造レベルは、MPSのハードウェアコンポーネントによって作成されます。

個々のデバイスの機能、それらの関係および情報について説明します

ストリーム。

ソフトウェアレベルは、2つのサブレベル(プロセッサ命令と

言語)およびMPSは、一連の演算子または

一部のデータ構造に対して1つまたは別のアクションを引き起こすコマンド。

論理レベルは、ディスクリートシステムにのみ固有であり、次のように分割されます。

2つのサブレベル:スイッチング回路とレジスタ転送。

最初のサブレベルは、ゲート(直並列回路とメモリ要素)とそれに基づいて構築されたデータ処理演算子によって形成されます。 2番目のサブレベルは、より高度な抽象化を特徴とし、レジスターの説明とレジスター間のデータ転送です。 2つ含まれています

部品:情報と制御:最初はレジスターによって形成され、

演算子とデータ転送パス、2番目はに依存して提供します

レジスタ間のデータ転送を開始する時報。

回路レベルは、ディスクリートデバイスの要素の動作の説明に基づいています。

MPSのライフサイクルには、他のディスクリートシステムと同様に、次の3つの段階があります。

設計、製造、運用。

各段階はいくつかの段階に細分され、構造的または物理的な障害が発生する可能性があります。 障害は、その原因に応じて分類されます。要素の欠陥が原因である場合は物理的であり、設計エラーが原因である場合は主観的です。

主観的な障害は、設計と対話型に分けられます。 設計

誤動作は、さまざまな段階でシステムに導入された欠陥によって引き起こされます

元のタスクの実装。 インタラクティブな障害はで発生します

サービス要員(オペレーター)の過失による作業のプロセス。 結果

誤動作の兆候はエラーであり、1つの誤動作は

多くのエラーを引き起こし、同じエラーが発生する可能性があります

多くの欠点。

欠陥の概念もあります-パラメータの物理的変化

範囲外のシステムコンポーネント。 欠陥は呼ばれます

一時的な場合は失敗し、永続的な場合は失敗します。

条件が作成されるまで、欠陥を検出することはできません。

それによる誤動作の発生、その結果は、それ自体であるはずです

キュー、作成するために調査対象オブジェクトの出力に渡されます

観察可能な障害。

トラブルシューティングは、エラーの原因を特定するプロセスです。

試験結果。

デバッグは、エラーを検出して判別するプロセスです。

MPSの設計におけるテストの結果に応じたそれらの発生源。

デバッグツールは、デバイス、コンプレックス、およびプログラムです。 時々下

デバッグは、障害の検出、ローカリゼーション、および除去を理解します。 成功

デバッグは、システムがどのように設計されているかによって異なります。

デバッグを容易にするプロパティ、および使用されるツール

デバッグ用。

デバッグのために、設計されたMPSは

可制御性、可観測性、予測可能性の特性。

管理性-その動作が影響を受けやすいシステムのプロパティ

管理、すなわち でシステムの動作を停止することが可能です

特定の状態になり、システムを再起動します。

可観測性-動作を追跡できるシステムのプロパティ

システム、その内部状態の変更後。

予測可能性–システムをインストールできるシステムのプロパティ

後続のすべての状態を予測できる状態。

MPSは、複雑さ、要件、および機能が大幅に異なる場合があります。

動作パラメータ、ソフトウェアの量、タイプ

マイクロプロセッサセットなど その結果、設計プロセスは

システムの要件に応じて変更します。

設計プロセスは反復プロセスです。 受け入れテスト段階で発見された誤動作は、仕様の修正につながる可能性があります。

したがって、システム全体の設計の最初に。 探す

誤動作はできるだけ早く必要です。 制御する必要があります

開発の各段階でのプロジェクトの正確さ。 以下の方法があります

設計管理:検証(形式手法

プロジェクトの正しさの証明); モデリング; テスト。

最近、ソフトウェア検証に関して多くの研究が行われています。

ソフトウェア、ファームウェア、ハードウェア。 しかし、これらの作品はまだです

理論的性格。 したがって、実際には、モデリングがより頻繁に使用されます

抽象のさまざまなレベルでのオブジェクトの動作とテスト

システムの表現。

システムの要件を形式化する段階で、プロジェクトの正確性を管理します

多くの設計目標が形式化されていないため、または

原則として形式化することはできません。 機能仕様は

専門家のチームによって分析されるか、モデル化およびテストされます

望ましい目標の達成を特定するための実験的順序。 承認後

機能仕様は、テストプログラムの開発を開始します。

に従ってシステムの正しい動作を確立するように設計されています

その仕様。 理想的には、テストは完全に開発されます

この仕様に基づいており、

機能を実行できると宣言されたシステムの実装

仕様で指定されています。 この方法は、他の方法とは正反対です。

テストは特定の実装用に構築されています。 ただし、実際には

テスト開発は、多くの場合、より低い優先順位が与えられます

プロジェクトなので、テストプログラムはそれよりずっと遅れて表示されます

マイクロプロセッサシステムの設計

構造

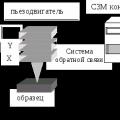

システムのブロック図を図3.2に示します。

図3.2-MPSのブロック図

MPはMPSの中心的なブロックです。 すべてのマイクロ回路を制御し、データ処理を実行します。

MPは米国でアドレスを生成し、SDSと交換します。

RAMは、中間データを格納するように設計されています。

ROMは、プログラムコードとさまざまな定数を格納するように設計されています。

PPIは、外部デバイスを接続するように設計されています。 ADC、ディスクリート信号、PPはPPIに接続されています。

ADCは、センサーからのアナログ信号をデジタルコードに変換するように設計されています。

PPは、制御室とMPの間のシリアルチャネルを介した交換を整理するように設計されています。

概略設計

MPSは以下を提供する必要があります。

- -7つのアナログセンサーの調査。

- -8つの離散信号の収集。

- -4つの個別の制御アクションの形成。

必要なデータメモリの量は、次の式を使用して計算されます

ここで、および-それぞれアナログおよびディスクリート入力信号の数。 および-アナログおよびディスクリート信号のビット深度。

私たちの場合、

その結果、センサーのポーリングデータを保存するには、

システムの中央処理装置としてKM1816BE51マイクロコントローラーが選択されました。 その主な利点は次のとおりです。

- -プログラムとデータの常駐メモリの可用性。

- -組み込みソフトウェアの存在。

- -4ポート;

- -低消費電力;

- -組み込みのタイマー-カウンター。

内蔵の128バイトのMKプログラムメモリがデータストレージに使用されます。 プログラムは常駐プログラムメモリに保存されます。

アナログセンサーの問い合わせには、K572PV4チップが使用されます。 マイクロチップのメリットは次のとおりです。

- -組み込みマルチプレクサの存在。

- -マイクロプロセッサの関与なしにセンサーの自動問い合わせ;

- -内蔵スタティックメモリに各チャネルの変換結果を保存します。

MKにはジェネレータ出力がないため、K531GG1ジェネレータチップを使用してクロック信号を生成します。

制御室との情報交換を整理するために、MCに組み込まれたトランシーバーが使用されます。 ただし、KM1816BE51ソフトウェアは、5ボルトの論理信号を使用してデータを送信します。1つは2.4Vから5Vの電圧レベルで表され、0は0から0.8 Vの電圧レベルで表されます。RS-232チャネルを介して送信する場合、0と1は同じ値(5〜12 V)でエンコードされていますが、符号が異なります。

RS-232伝送では、5ボルトの論理信号を別のレベルに変換する必要があるため、MPSはマキシムのMAX202Eチップを使用します。 + 5Vから±10Vまでの電圧コンバーターと、RS-232規格に準拠した標準の5ボルトレベルのロジック信号を変換するカスケードが含まれています。 2つのレシーバーと2つのトランスミッター用のロジックレベルコンバーターが含まれており、そのうち1つのトランシーバーチャネルのみが使用されます。

MPSの概略図を付録Bに示します。

12 MHzのZQ1水晶振動子は、DD1マイクロコントローラーのXTAL1ピンとXTAL2ピンに接続されています。 より安定した始動のために、水晶振動子の出力は、21pFの容量のコンデンサC1とC2を介して共通のワイヤに接続されます。

マイクロコントローラに供給電圧が印加されている場合は、マイクロコントローラをリセットする必要があります。 この目的のために、RST入力は6μFのコンデンサC3を介して電源バスに接続され、100kΩの抵抗R1を介して共通ワイヤに接続されます。 電源投入時にコンデンサが放電され、リセット入力は電源電圧に近い電位になります。 C3の充電によりこの電位が低下したにもかかわらず、10ミリ秒の間、リセット入力の信号レベルは1のままであり、マイクロコントローラーは正しく起動します。

論理単位が入力に適用されます。 マイクロコントローラは常駐メモリからプログラムを実行します。

ディスクリート入力信号DDAT1-DDAT8は、MKDD1のポートP0のラインに接続されています。 ACSDA1はポートP1の回線に接続されています。 個別の制御アクションDOUT1-DOUT4は、ラインP1.0-P1.3に形成されます。

ACS DA1に接続されているアナログセンサーには、0V〜2.5Vの範囲の出力電圧パラメーターが必要です。 抵抗R2〜R13は、センサーの電流信号を電圧信号に変換するために使用されます。

要素の仕様は付録Dに示されています。

MPS操作アルゴリズムの開発

MPSは次の順序で機能します。

- a)システムの初期化。

- b)センサーへの問い合わせ。

- c)ポンプユニットの制御。

- d)制御室とのデータ交換。

- e)ステップbに進みます。

MPS作業プログラムのアルゴリズムのブロック図を付録Eに示し、プログラムコードの一部を付録Eに示します。

消費電力の計算

システム全体で消費される電力は、システムのすべての部分で消費される電力の合計として定義されます。

電力計算は表3.4にまとめられています。

表3.1-消費電力の計算

システムは電力を消費しています。

通信機器

MI 486インターフェースコンバーターは、制御室との交換を確実にするために使用され、イーサネットネットワークを介してコンピューターから最大112kbaudの速度でデータを送受信できます。

インターフェースコンバーターを図3.3に示します。

図3.3-インターフェースコンバーターMI486

仕様:

- -出力インターフェース:RS-232;

- -最大 速度-最大112kbaud;

- -入力インターフェイスイーサネット10BaseT / 100BaseT;

- -RJ45コネクタ。

GIS処理プログラムの選択

GIS処理プログラムの選択 交流の電気回路の計算と分析

交流の電気回路の計算と分析 走査型プローブ顕微鏡走査型プローブ顕微鏡の現状と発展

走査型プローブ顕微鏡走査型プローブ顕微鏡の現状と発展