Mikrokontroleri MCS-51: softverski model, struktura, naredbe. Mikrokontroleri MCS-51: programski model, struktura, naredbe Mikrokontroleri iz obitelji mcs 51

Osnova mikrokontrolera (vidi sliku 1) je 8-bitna aritmetičko-logička jedinica (ALU). Memorija MK ima harvardsku arhitekturu, t.j. logički podijeljena: na programsku memoriju - PP (internu ili eksternu), adresiranu 16-bitnim brojačem naredbi (SC) i memoriju podataka - internu (Resident data memory - RPD) 128 (ili 256) bajtova, kao i eksternu (External podatkovna memorija – VPD) do 64 KB. Fizički, programska memorija je implementirana na ROM (samo za čitanje), a memorija podataka implementirana je na RAM (podaci se mogu pisati i čitati).

Prijem i isporuka vanjskih signala vrši se preko 4 osmobitna porta R0..R3. Prilikom pristupa vanjskoj programskoj memoriji (EPM) ili podatkovnoj memoriji (VPD), portovi P0 i P2 se koriste kao multipleksirana vanjska sabirnica adresa/podataka. Linije P3 porta također mogu obavljati alternativne funkcije (vidi tablicu 1).

16-bitni DPTR registar čini VPD adresu ili osnovnu adresu programske memorije u uputama za pretvorbu akumulatora. DPTR registar se također može koristiti kao dva nezavisna 8-bitna registra (DPL i DPH) za pohranjivanje operanada.

8-bitni interni registar naredbi (RK) prima kod naredbe koja se izvršava; ovaj kod dekodira upravljački krug, koji generira upravljačke signale (vidi sliku 1).

Pristup registrima posebnih funkcija - RSF (SFR - na slici 1. zaokruženi su isprekidanom linijom) moguć je samo korištenjem izravnog bajtova adresiranja u rasponu adresa od 128 (80h) i više.

Stalna podatkovna memorija (RDD) u prvim modelima mikrokontrolera obitelji MCS-51 imala je kapacitet od 128 bajtova. Donja 32 bajta RPD-a također su registri opće namjene - RON (4 banke po 8 RON). Program se može prijaviti na jedan od 8 RON-a aktivne banke. Odabir aktivne banke RON-ova provodi se programiranjem dva bita u registru statusa procesora - PSW.

Tablica 1 - Dodjela pinova MCS-51

| Pin br. | Oznaka | Svrha |

| 1..8 | P1 | 8-bitni kvazi-dvosmjerni I/O port |

| 9 | RST | Reset signal (aktivna razina - visoka); RST signal se resetuje: PC i većina registara posebnih funkcija (SFR), onemogućujući sve prekide i mjerače vremena; odabire RON Bank 0; upisuje "sve one" na portove P0_P3, pripremajući ih za unos; upisuje kod 07H u pokazivač steka (SP); |

| 10..17 | 8-bitni kvazi-dvosmjerni I/O port; nakon upisa u odgovarajući bit "1" - obavlja dodatne (alternativne) funkcije: Ulaz serijskog porta - RxD; Izlaz serijskog porta - TxD; Ulaz vanjskog prekida 0 - ~INT0; Ulaz vanjskog prekida 1 - ~INT1; Tajmer/brojač ulaz 0 - T0; Tajmer/brojač ulaz 1 - T1; Strobe izlaz. signal prilikom pisanja u VPD - ~ WR; Strobe izlaz. signal pri čitanju iz VPD-a - ~ RD; |

|

| 18, 19 | X1, X2 | Zaključci za spajanje kvarcnog rezonatora ili LC kruga; |

| 20 | GND | Opći zaključak; |

| 21..28 | P2 | 8-bitni kvazi-dvosmjerni I/O port; ili izlazna adresa A u načinu rada vanjske memorije (VPP ili VPD); |

| 29 | PME | Strobe za čitanje vanjske programske memorije, izdaje se samo pri pristupu vanjskom ROM-u; |

| 30 | PIVO | Adresni strobosjek vanjske memorije (VPP ili VPD); |

| 31 | EA | Onemogućujući RPP, razina "0" na ovom ulazu prebacuje MK na odabir naredbi samo sa piste ; |

| 39..32 | P0 | 8-bitni dvosmjerni I/O port; kada pristupa vanjskoj memoriji, izdaje adrese A (koje su upisane u vanjski registar pomoću ALE signala), a zatim sinkrono razmjenjuje bajt sa signalom ~PME (za naredbe) ili ~WR,~RD (za podatke u VPD-u) , pri pristupu vanjskoj memoriji sve jedinice se upisuju u registar porta P0, uništavajući tamo pohranjene informacije; |

| 40 | Ucc | Izlazni napon napajanja |

Prebacivanje banaka RON-ova pojednostavljuje izvršavanje potprograma i rukovanje prekidima, jer. nije potrebno prenositi sadržaj RON-ova glavnog programa u stog prilikom pozivanja potprograma (dovoljno je otići u drugu aktivnu RON banku u potprogramu).

Pristup RPD-u je moguć korištenjem neizravnog ili izravnog bajtova adresiranja (izravno adresiranje bajtova omogućuje pristup samo prvih 128 bajtova RPD-a).

Prošireno RPD područje (za mikrokontrolere obitelji MCS-52 i sljedeće obitelji) od adrese 128 (80h) do 255 (FFh) može se adresirati samo korištenjem metode neizravnog adresiranja.

Tablica 2 - Blok registri posebnih funkcija (s f r)

| Mnemo kod | Ime | |

| 0E0h | *ACC | Baterija |

| 0F0h | *B | Registrirajte ekspander baterije |

| 0D0h | *PSW | Riječ statusa procesora |

| 0B0h | *P3 | luka 3 |

| 0A0h | * P2 | luka 2 |

| 90h | * P1 | Luka 1 |

| 80h | *P0 | Port 0 |

| 0B8h | * IP | Registar prioriteta prekida |

| 0A8h | *IE | Registar maske prekida |

| 99h | SBUF | Međuspremnik serijskog primopredajnika |

| 98h | * SCON | Registar kontrole/statusa serijskog porta |

| 89h | TMOD | Registar načina rada mjerača/brojača |

| 88h | * TCON | Registar mjerača vremena/upravljanja brojačem/statusa |

| 8Dh | TH1 | Tajmer 1 (visoki bajt) |

| 8bh | TL1 | Tajmer 1 (niski bajt) |

| 8h | TH0 | Tajmer 0 (visoki bajt) |

| 8ah | TL0 | Tajmer 0 (niski bajt) |

| 83h | DPH | Registar pokazivača podataka (DPTR) (visoki bajt) |

| 82h | DPL | Registar pokazivača podataka (DPTR) (niski bajt) |

| 81h | SP | Registar pokazivača steka |

| 87h | PCON | Registar kontrole snage potražnje |

2. SOFTVERSKI MODEL MCS–51

VRSTE NAREDBA MCS–51

Gotovo polovica naredbi se izvršava u jednom strojnom ciklusu (MC). Uz frekvenciju kristalnog oscilatora od 12 MHz, vrijeme izvršenja takve naredbe je 1 μs. Preostale naredbe se izvode u 2 strojna ciklusa, tj. za 2 ms. Samo instrukcije množenja (MUL) i dijeljenja (DIV) izvode se u 4 strojna ciklusa.

Tijekom jednog strojnog ciklusa, postoje dva pristupa programskoj memoriji (unutarnja ili vanjska) za čitanje dva bajta instrukcije ili jedan pristup vanjskoj memoriji podataka (EDM).

3. METODE (METODE) ODRŠAVANJA MCS–51

1. ADRESIRANJE REGISTRA - 8-bitni operand nalazi se u RON odabrane (aktivne) banke registara;

2 IZRAVNO ADRESIRANJE (označeno znakom - #) - operand se nalazi u drugom (a za 16-bitni operand i u trećem) bajtu naredbe;

3 NEIZRAVNO ADRESIRANJE (označeno znakom - @) - operand se nalazi u memoriji podataka (RPD ili VPD), a adresa memorijske ćelije je sadržana u jednom od RON-ova neizravnog adresiranja (R0 ili R1); u naredbama PUSH i POP, adresa je sadržana u pokazivaču steka SP; DPTR registar može sadržavati VPD adresu do 64K;

4 DIRECT BYTE ADDRESSING – (dir) – koristi se za pristup RPD ćelijama (adrese 00h…7Fh) i registrima posebnih funkcija SFR (adrese 80h…0FFh);

5 IZRAVNO BITSKO ADRESIRANJE - (bit) - koristi se za adresiranje odvojeno adresabilnih 128 bitova smještenih u RPD ćelijama na adresama 20H ... 2FH i za odvojeno adresibilne bitove posebnih funkcijskih registara (vidi tablicu 3 i model programa);

6 INDIREKTNO INDEKSNO ADRESIRANJE (označeno znakom @) - pojednostavljuje pregled tablica u programskoj memoriji, PP adresa je određena zbrojem osnovnog registra (PC ili DPTR) i indeksnog registra (Battery);

7 IMPLICITNO (UGRAĐENO) ADRESIRANJE - kod instrukcije sadrži implicitnu (po defaultu) referencu na jedan od operanada (najčešće na Akumulator).

4. FORMAT RIJEČI STANJA PROCESORA (PSW).

C - Carry (CARY) ili posudila zastavica, također funkcionira kao "boolean akumulator" u bit-operiranim uputama;

AC – pomoćna (dodatna) oznaka prijenosa – postavljena na "1" ako je naredba za zbrajanje (ADD, ADDC) imala prijenos s tetrade nižeg reda na visoki red (tj. iz 3. bita u 4. bit);

F0 - korisnička zastavica - postavljena, resetirana i provjerena softverom;

| RS1 | RS0 | Banka | Adresa (direktor) |

| 0 | 0 | 0 | 00h..07h |

| 0 | 1 | 1 | 08h..0Fh |

| 1 | 0 | 2 | 10h..17h |

| 1 | 1 | 3 | 18h..1Fh |

RS1,RS0 – Odabir banke registracije:

OV - Zastavica aritmetičkog preljeva; njegova je vrijednost određena XOR operacijom ulaznih i izlaznih prijenosnih signala najznačajnijeg bita ALU-a; jedna vrijednost ove zastavice označava da je rezultat aritmetičke operacije u komplementarnom kodu dva izvan raspona: –128…+127; prilikom izvođenja operacije dijeljenja, OV zastavica se resetira, a u slučaju dijeljenja na nulu postavlja se; prilikom množenja, OV zastavica se postavlja ako je rezultat veći od 255 (0FFH);

Bit PSW - rezerviran, sadrži okidač, dostupan za pisanje ili čitanje;

P - zastavica parnosti - je zbrajanje broja pojedinačnih bitova u akumulatoru paran broj; formira se kombinacijskim krugom (programski dostupan samo za čitanje).

Mikrokontroleri MCS-51 nemaju oznaku "Z". Ali u uputama za uvjetni skok (JZ, JNZ), kombinacijski sklop provjerava trenutni (nula ili ne-nula) sadržaj akumulatora.

Sve naredbe prijenosa i razmjene operanada mogu se izvesti preko Akumulatora (vidi sliku 3). Štoviše, prijenosi iz/u vanjsku memoriju (programska memorija ili memorija podataka) mogu se izvesti samo putem baterije.

Većina prijenosa također se može izvršiti putem proslijeđenog bajta (dir). Postoje čak i prijenosi dir-to-dir (vidi sliku 3).

Prijenosi koji nedostaju iz RON u RON mogu se implementirati kao prijenosi iz RON u proslijeđeni bajt dir (s obzirom da se RON-ovi nalaze u početnom području stalne memorije podataka, čije se ćelije mogu adresirati kao dir).

XCH naredbe za razmjenu omogućuju vam slanje bajtova bez uništavanja oba operanda.

Aritmetičke naredbe se izvršavaju samo u Akumulatoru. Stoga se prvi operand prvo mora staviti u Akumulator, a zatim dodati ili oduzeti drugi operand. Rezultat se stavlja u Akumulator.

Naredba za oduzimanje SUBB-a se izvršava samo uz posudbu (tj. Cary zastavica također se oduzima od rezultata). Stoga, da bi se izvršila instrukcija oduzimanja bez posuđivanja, potrebno je prvo izvršiti Clear Flag C (CLRC) instrukciju.

Instrukcija za množenje jednobajtnih operanda - MULAB - postavlja dvobajtni (16-bitni) rezultat: niži bajt je u Akumulatoru, a visoki bajt je u registru B.

Rezultat izvršavanja instrukcije za dijeljenje jednobajtnih operanda - DIVAB - stavlja se: količnik - akumulator, ostatak - u registar B.

INC aritmetička instrukcija dodaje jedan odabranom operandu. Aritmetička instrukcija DEC oduzima jedan od odabranog operanda. Akumulatorska decimalna ispravka (DAA) instrukcija pomaže vam da dodate binarno kodirane decimalne (BCD) brojeve bez pretvaranja u heksadecimalni (hex) format. Izvorni operandi moraju biti u BCD formatu, tj. u svakoj tetradi od jednog bajta nalaze se samo brojevi od 0 do 9 (ne mogu biti heksadecimalni brojevi: A, B, C, D, E, F). Stoga jedan bajt može sadržavati brojeve od 00 do 99 za pakirane BCD brojeve ili brojeve od 0 do 9 za nepakirane BCD brojeve.

Naredba DA A - decimalni ispravak izvodi radnje na sadržaju Akumulatora nakon dodavanja BCD brojeva u procesoru (brojevi su dodani prema zakonima heksadecimalne aritmetike) na sljedeći način (vidi primjer):

· ako je sadržaj tetrade nižeg reda akumulatora veći od 9 ili je postavljena pomoćna zastavica za nošenje (AC = 1), tada se sadržaju akumulatora dodaje 6 (odnosno šest znamenki koje nedostaju u heksadecimalnom format);

· ako je nakon toga sadržaj višeg reda Akumulatora veći od 9 ili je postavljena zastavica C, tada se broj 6 dodaje visokom redu Akumulatora.

Instrukcija decimalnog ispravljanja DA A ne koristi se nakon instrukcije inkrementa (INC) jer instrukcija povećanja ne utječe (mijenja) na zastavice C i AC.

Logičke naredbe:

Logično "I" - ANL,

Logično "ILI" - ORL,

Logička naredba XOR - XRL - se izvršava u Akumulatoru (kao i aritmetika), ali je moguće izvršiti i logičke naredbe u bajtu izravne adrese (dir). U ovom slučaju, drugi operand može biti:

u bateriji ili

Neposredni operand u instrukciji.

Upute za rotaciju (RR A, RL A) i upute za rotaciju kroz CARY zastavu (RRC A, RLC A) rotiraju sadržaj Akumulatora za 1 bit. Bitovi se operandi šalju samo preko zastavice C.

Arhitektura obitelji MCS-51 uvelike je predodređena njenom namjenom - građevinom kompaktan i jeftino digitalnih uređaja. Sve funkcije mikroračunala implementirane su pomoću jednog mikrosklopa. Obitelj MCS-51 uključuje cijeli niz mikro krugova od najjednostavnijih mikrokontrolera do prilično složenih. Mikrokontroleri iz obitelji MCS-51 omogućuju vam obavljanje zadataka upravljanja raznim uređajima i implementacije pojedinačnih čvorova analognog kruga. Svi mikro krugovi ove obitelji rade s istim zapovjedni sustav MCS-51, većina ih se izvodi u istim slučajevima s odgovarajući pinout(numeracija nogu za kućište). To vam omogućuje da za razvijeni uređaj koristite čipove različitih tvrtki - Maxim, Atmel, NXP itd. (catalog..php?page=components_list&id=39"> s.m. Pretraživanje po parametrima) bez mijenjanja sklopne sheme uređaja i programa.

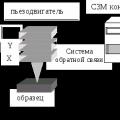

Slika 1. Blok dijagram I8751 kontrolera

Blok dijagram kontrolera prikazan je na slici 1 i sastoji se od sljedećih glavnih funkcionalnih jedinica: upravljačke jedinice, aritmetičko-logičke jedinice, jedinice timera/brojila, serijskog sučelja i jedinice za prekid, programskog brojača, memorije podataka i programska memorija. Bilateralna razmjena provodi se pomoću interne 8-bitne autoceste podataka.

Pogledajmo pobliže svrhu svakog bloka. Gotovo svi predstavnici obitelji MCS-51 izgrađeni su prema ovoj shemi.. Različiti mikro krugovi ove obitelji razlikuju se samo po registrima posebne namjene (uključujući broj priključaka). Sustav zapovijedanja svih kontrolera iz obitelji MCS-51 sadrži 111 osnovnih naredbi s formatom od 1, 2 ili 3 bajta i ne mijenja se pri prelasku s jednog čipa na drugi. To osigurava izvrsnu prenosivost programa s jednog čipa na drugi.

Jedinica za upravljanje i sinkronizaciju

Jedinica za upravljanje i sinkronizaciju (Timing and Control) dizajnirana je za generiranje sinkronizacijskih i upravljačkih signala koji osiguravaju koordinaciju zajedničkog rada OEVM jedinica u svim dopuštenim načinima rada. Upravljačka jedinica uključuje:

- - uređaj za formiranje vremenskih intervala,

- - I/O logika,

- - registar instrukcija,

- - registar upravljanja potrošnjom električne energije,

- - dekoder naredbi, računalna upravljačka logika.

Uređaj za određivanje vremena namijenjen je za generiranje i izlaz internih sinkronizacijskih signala faza, ciklusa i ciklusa. Broj strojnih ciklusa određuje trajanje izvršenja instrukcije. Gotovo sve OEVM naredbe izvode se u jednom ili dva strojna ciklusa, osim naredbi za množenje i dijeljenje čije trajanje je četiri strojna ciklusa. Označimo frekvenciju glavnog oscilatora kroz F g. Tada je trajanje strojnog ciklusa 12/F g, odnosno 12 perioda signala glavnog oscilatora. Ulazno-izlazna logika je dizajnirana za primanje i izdavanje signala koji osiguravaju razmjenu informacija s vanjskim uređajima kroz ulazno/izlazne portove P0-P3.

Zapovjedni registar dizajniran je za snimanje i pohranjivanje 8-bitnog operacijskog koda naredbe koja se izvršava. Operativni kod se uz pomoć dekodera naredbi i računalne upravljačke logike pretvara u mikroprogram za izvršavanje naredbi.

Registar kontrole potražnje (PCON) omogućuje vam da zaustavite rad mikrokontrolera kako biste smanjili potrošnju energije i smanjili razinu smetnji od mikrokontrolera. Još veće smanjenje potrošnje energije i smanjenje buke može se postići zaustavljanjem glavnog oscilatora mikrokontrolera. To se može postići prebacivanjem bitova u registru upravljanja potražnjom PCON. Za n-MOS proizvodnu opciju (serija 1816 ili strani čipovi koji nemaju slovo "c" u sredini imena), PCON registar kontrole snage sadrži samo jedan bit koji kontrolira brzinu prijenosa SMOD serijskog porta, i nema bitova za kontrolu snage.

Aritmetičko-logička jedinica (ALU) je paralelni osmobitni uređaj koji pruža aritmetičke i logičke operacije. ALU se sastoji od:

- - registri akumulatora, registri za privremenu pohranu TMP1 i TMP2,

- - ROM konstante,

- - guja,

- - dodatni registar (registar B),

- - akumulator (ACC),

- - registar statusa programa (PSW).

Registar baterija i držanje registara- osmobitni registri dizajnirani za primanje i pohranjivanje operanada za vrijeme trajanja operacija na njima. Ovi registri nisu programski dostupni.

ROM konstante osigurava razvoj ispravljačkog koda za binarno-decimalni prikaz podataka, koda maske za bitne operacije i konstantnog koda.

Paralelni 8-bitni zbrajač je kombinacijski sklop sa sekvencijalnim prijenosom, dizajniran za izvođenje aritmetičkih operacija zbrajanja, oduzimanja i logičkih operacija zbrajanja, množenja, dispariteta i identičnosti.

Registar B- osmobitni registar koji se koristi tijekom operacija množenja i dijeljenja. Za ostale upute može se smatrati dodatnim registrom scratchpad-a.

Baterija- osmobitni registar dizajniran za primanje i pohranjivanje rezultata dobivenog prilikom izvođenja aritmetičko-logičkih operacija ili operacija pomaka

Serijsko sučelje i blok prekida (SIP) dizajniran je za organiziranje ulazno-izlaznih sekvencijalnih tokova informacija i organiziranje sustava prekida programa. Blok uključuje:

- - PIP međuspremnik,

- - upravljačka logika,

- - kontrolni registar,

- - međuspremnik odašiljača,

- - međuspremnik prijemnika,

- - serijski primopredajnik,

- - registar prioriteta prekida,

- - registar omogućavanja prekida,

- - logika za obradu zastavica prekida i shema generiranja vektora.

Brojač programa je dizajniran da formira trenutnu 16-bitnu adresu interne programske memorije i 8/16-bitnu adresu vanjske programske memorije. Programski brojač sastoji se od 16-bitnog PC međuspremnika, PC registra i inkrementnog kruga (povećava sadržaj za 1).

Podatkovna memorija (RAM) namijenjen je za privremeno pohranjivanje informacija koje se koriste tijekom izvođenja programa.

Priključci P0, P1, P2, P3 su kvazi-dvosmjerni ulazno-izlazni portovi i dizajnirani su da osiguraju razmjenu informacija između OEVM-a i vanjskih uređaja, tvoreći 32 ulazno-izlazne linije.

Tajmer uređaj Osnovni modeli obitelji imaju dva programabilna 16-bitna mjerača vremena/brojila (T/C0 i T/C1) koji se mogu koristiti i kao mjerači vremena i kao vanjski brojači događaja.

Registar statusa programa (PSW) dizajniran je za pohranu informacija o stanju ALU-a tijekom izvođenja programa.

Programska memorija (EPROM) dizajniran za pohranjivanje programa i memorija je samo za čitanje (ROM). Razni mikro krugovi koriste maskirane ROM-ove koji se brišu ultraljubičastim zračenjem odn BLJESAK ROM.

Registar pokazivača podataka (DPTR) dizajniran je za pohranjivanje 16-bitne adrese vanjske memorije podataka ili programske memorije.

Pokazivač steka (SP) je osmobitni registar dizajniran da organizira posebno područje memorije podataka (stog) u koje se može privremeno pohraniti bilo koja memorijska ćelija.

Stanje sustava prekida se ispituje na kraju svakog strojnog ciklusa u fazi S5P2, s izuzetkom RETI instrukcija i svih instrukcija koje pristupaju IE i IP registrima. Potrebno je 38 do 86 periodi frekvencije fOSC od trenutka predaje zahtjeva za prekidom do servisiranja prekida, ovisno o fazi zahtjeva i broju strojnih ciklusa instrukcije tijekom kojih je zahtjev primljen.

Kada se prekid implementira u hardver, izvršava se instrukcija LCALL addr16, koja osigurava da se trenutno stanje programskog brojača pohrani na stog (pamti povratnu adresu) i skače na početnu adresu addr16 odgovarajuće servisne procedure. Svaki izvor zahtjeva za prekid ima svoju pridruženu vezu

početna adresa (vektor prekida): |

||||

Vanjski prekid INT0. |

||||

Prekid mjerača/brojača TC0. |

||||

Vanjski prekid INT1. |

||||

Prekid mjerača/brojača TC1. |

||||

Prekid serijskog porta. |

||||

2.7. Metode adresiranja i sustav zapovijedanja obitelji MCS-51

Zapovjedni sustav obitelji MCS-51 usmjeren je na organiziranje fleksibilnog unosa/izlaza podataka kroz univerzalne portove P0...P3 i primarnu obradu informacija. Posebna se pozornost posvećuje operacijama s bitovima i prijenosu kontrole po njihovoj vrijednosti. Instrukcije koje izvode takve operacije čine veliku skupinu i zajedno s pripadajućim hardverom tvore takozvani "Boolean procesor" kao dio MCS-51 arhitekture.

Sustav naredbi omogućuje programeru mogućnost korištenja većine operacija s punim skupom metoda adresiranja i hardverskih resursa dostupnih softveru.

2.7.1. Metode adresiranja

Svaka instrukcija govori procesoru operaciju koju treba izvesti i metode za pristup operandima. Kod naredbe ima nekoliko polja koja imaju određenu funkcionalnu svrhu. Najvažnija polja svake naredbe su šifra operacije (COP), koja određuje djelovanje naredbe, i adresni dio. Polja adresnog dijela sadrže informacije o adresama operanda i rezultatu operacije, au nekim slučajevima i informaciju o adresi sljedeće instrukcije.

Ako adresa ukazuje na broj memorijske ćelije u kojoj se operand nalazi ili gdje je upisan, tada se naziva izravna adresa.

Metode adresiranja su skup mehanizama za pristup operandima. Neki od njih su jednostavni, što rezultira kompaktnim formatom instrukcija i brzim pristupom operandu, ali imaju ograničenu količinu dostupnih resursa. Drugi vam omogućuju rad sa svim resursima dostupnim u sustavu, ali se naredba ispostavilo da je duga,

unos i izvođenje troši se puno vremena. Skup metoda adresiranja u svakom skupu instrukcija je kompromisna kombinacija poznatih mehanizama adresiranja koje su odabrali dizajneri arhitekture na temelju skupa zadataka koje treba riješiti.

Sljedeće su glavne metode adresiranja koje se koriste u obiteljskom naredbenom sustavu MCS-51.

Implicitno adresiranje. Naredba ne sadrži eksplicitne naznake o adresi operanda koji sudjeluje u operaciji ili adresi na kojoj se nalazi rezultat operacije, ali se ta adresa podrazumijeva. U naredbama se akumulator najčešće implicitno adresira kao odredište rezultata operacije. Na primjer, rezultat zbrajanja sadržaja akumulatora (A) i registra R1 tekuće banke podataka naredbom ADD A,R1 zapisuje se u implicitno adresirani akumulator. Cijela navedena instrukcija zauzima jedan bajt u memoriji, dok adresa samo akumulatora (8Eh SFR područja) sadrži jedan bajt.

Izravno oslovljavanje. U adresnom polju naredbe sadrži

Ne živi adresa operanda, već sam operand. Izravno adresiranje je označeno posebnim znakom # ispred broja. Na primjer, naredba MOV A,#15h učitava heksadecimalni broj 15 (drugi bajt naredbe) u akumulator. U sustavu naredbi, izravno adresiranje se označava kao #data, gdje je podatak broj

(podaci = 00h...FFh).

Izravno oslovljavanje. Polje adrese instrukcije specificira izravnu adresu memorijske lokacije podataka u kojoj se nalazi operand ili gdje je zapisan. Na primjer, MOV A,15h instrukcija učitava sadržaj DSEG ćelije na adresi 15h u akumulator. Memorijska ćelija je izravno adresabilna, dok je akumulator implicitno adresiran. Ovisno o mjestu adresiranog operanda, izravno adresiranje se dijeli na registrsko izravno adresiranje i apsolutno adresiranje.

Izravno adresiranje registra. Polje adrese naredbe sadrži izravnu adresu registra trenutne banke registara. U svakoj banci postoji osam registara, a za njihovo adresiranje potrebna je trobitna izravna adresa. U mnemotehnici naredbi adresabilni registar označava se s Rn, gdje je n=0...7. Sva polja naredbe staju u jedan bajt. Takvo oslovljavanje naziva se kratko. Na primjer, MOV R4, R1.

Izravno apsolutno adresiranje omogućuje vam pristup bilo kojoj DSEG ćeliji i SFR području. Izravna adresa u ovom slučaju zauzima jedan bajt, a naredba dva bajta. U sustavu naredbi bajt izravne adrese označava se riječju izravno (izravno) (izravno = 00h ... FFh). Na primjer, instrukcija MOV 80h,R2 (ili MOV P0,R2) učitava sadržaj registra R2 tekuće banke podataka u port P0 (lokacija 80h SFR-a). Ako su oba operanda izravno apsolutna adresabilna, tada instrukcija postaje trobajtna instrukcija (npr. MOV 80h,15h).

neizravno oslovljavanje. Adresno polje sadrži adresu memorijske lokacije na kojoj se nalazi izravna adresa operanda. U sustavu naredbi, neizravno adresiranje je označeno posebnim znakom @. imovine

registri R0 i R1 (@Ri, i = 0,1) svake banke registara moraju pohraniti izravnu adresu. Na primjer, ako je sadržaj registra R1 trenutne banke registra 15h, tada će instrukcija MOV A,@R1 izvesti istu radnju kao gornja instrukcija MOV A,15h - učitat će sadržaj DSEG memorijske lokacije sa adresom 15h u akumulator. Međutim, naredba MOV A, @ R1 je jednobajtna, ali što je najvažnije, moguće je programski promijeniti adresu promjenom sadržaja registra R1.

Relativno oslovljavanje. Kod relativnog adresiranja, izravna adresa se formira dodavanjem osnovne adrese adresnom polju naredbe. Sadržaj programskog brojača koristi se kao osnovna adresa, a adresno polje instrukcije je osmobitni rel (relativni) pomak. Rel broj se naredbom tumači kao predpisani cijeli broj predstavljen u komplementu dva. Njegov raspon prezentacije je (-128...+127). Prilikom određivanja rel broja, imajte na umu da programski brojač pokazuje na sljedeću instrukciju koju treba izvršiti. Relativno adresiranje se naširoko koristi u naredbama prijenosa upravljanja, što omogućuje stvaranje premjenjivih programskih modula. Naredbe prijenosa upravljanja s relativnim adresiranjem dopuštaju grananje u odnosu na trenutni položaj brojača PC programa u oba smjera za (-128...+127) bajtova.

U programima asemblerskog jezika, polje pomaka može se koristiti za određivanje oznake na koju treba skočiti. Kao rezultat prijevoda, asembler će izračunati vrijednost pomaka ako ne prelazi (-128…+127). U suprotnom će se izdati poruka o pogrešci.

Osnovno adresiranje predstavlja svojevrsno relativno adresiranje. Izravna adresa u ovom slučaju se formira dodavanjem adrese navedene u naredbi sadržaju osnovnog registra, koji pohranjuje osnovnu adresu. Funkciju osnovnog registra u obitelji MCS-51 obavlja registar pokazivača podataka DPTR ili brojač PC programa. Ova vrsta adresiranja posebno je korisna pri obradi tablica i nizova podataka. U uputama MOVC A,@A+DPTR i MOVC A,@A+PC, 16-bitna izravna adresa formira se kao zbroj sadržaja DPTR i A ili PC i A registara.

Addressing stranica. Kada se koristi adresiranje stranica, memorija se dijeli na više stranica iste duljine. Adresiranje stranica provodi se posebnim registrom stranica, a memorijske ćelije unutar stranice adresiraju se adresom sadržanom u instrukciji. Izravna adresa se formira spajanjem (pripajanjem) adrese stranica i adrese memorijske ćelije unutar stranice. U instrukciji MOVX A,@Ri, port P2 (visoki bajt adrese) obavlja funkciju registra stranice, a sadržaj registra Ri (niski bajt adrese) specificira adresu unutar stranice. U ovom slučaju, memorija je podijeljena na 256 stranica od 256 ćelija u svakoj od njih.

Adresiranje steka koristi se u bezadresnim naredbama i kombinacija je metoda adresiranja s auto-inkrementom i auto-dekrementom, koji rade na principu LIFO (L ast I nput - F irst O izlaz) - “posljednji ušao – prvi izašao”. Stog se nalazi u DSEG-u i raste u smjeru povećanja adrese. Adresa vrha hrpe nalazi se u pokazivaču steka SP. Kada se bajt gurne u stog, prvo se povećava sadržaj SP-a, a zatim se upisuje adresa. Prilikom čitanja bajta iz steka, prvo pročitajte na adresi na koju ukazuje SP, a zatim smanjite SP. Kada koristite stog, imajte na umu da dubinu stoga (maksimalni broj memorijskih ćelija koje zauzima stog) ne kontrolira hardver. S prekomjernim povećanjem hrpe, memorijske ćelije koje nisu namijenjene za to mogu biti zaokupljene gubitkom informacija u njima. Hardverski stog se koristi za pohranjivanje povratne adrese prilikom servisiranja prekida.

2.7.2. Obiteljski zapovjedni sustav MCS-51

Sustav naredbi prikazan je u tablicama A2.1...A2.6 Dodatka 2. Tablice pokazuju naziv naredbe, njen mnemonički, binarni operacijski kod, učinak izvršene naredbe na zastavice C, OV, AC i P, duljina naredbe u bajtovima (B) i vrijeme izvršenja u strojnim ciklusima (C), kao i sadržaj pretvorbe koju izvodi instrukcija. Zarez se koristi kao razdjelnik za adresna polja u naredbama. Da bi se poboljšala čitljivost, razmaci se mogu dodati nakon zareza ako to podržava asembler koji se koristi.

Cijeli skup naredbi može se podijeliti u 5 grupa: operacije prijenosa podataka, aritmetičke operacije, logičke operacije, operacije s bitovima i operacije prijenosa kontrole.

Grupa naredbi operacije prijenosa podataka(Tablica A2.1) ko-

drži MOV naredbe (prijenos podataka između DSEG-a i RSEG-a), MOVC (između CSEG-a i A), MOVX (između XSEG-a i A), PUSH i POP naredbe za pristup stogu i dvije naredbe za razmjenu XCH i XCHD. Sve upute za prijenos podataka čije je odredište akumulator postavljaju zastavicu parnosti P sadržaja akumulatora, a upute za izravnu adresu čije je odredište PSW registar mijenjaju sve zastavice. Najopsežnija je instrukcija MOV, koja koristi četiri metode adresiranja: izravni registar (A, Rn, DPTR), izravni (izravni), neizravni (@Ri), izravni (#data, #data16). Drugi operand naredbe je izvor, prvi operand je odredište. Postoje tri metode adresiranja (osim izravnog) za određivanje odredišta i sve četiri za određivanje izvora. Trobajtna MOV izravna, izravna instrukcija osigurava prijenos između bilo koje dvije memorijske ćelije (DSEG i SFR), uključujući RSEG. Za razmjenu s RSEG-om predviđeni su posebni dvo- i jednobajtni formati:

Posebna instrukcija MOV DPTR,#data16 učitava 16-bitni DPTR pokazivač s vrijednošću data16.

MOVC instrukcija omogućuje čitanje informacija iz memorije programa CSEG ne u registar naredbi upravljačkog uređaja, već u akumulator operativnog uređaja. Naredba koristi dvije metode adresiranja: na temelju DPTR-a i u odnosu na PC. U oba slučaja, nepredznačeni cjelobrojni pomak (indeks) pohranjuje se u akumulator. Akumulator također služi kao prijemnik rezultata. Naredba vam omogućuje brzo rekodiranje po tablicama.

Vanjskoj memoriji se pristupa pomoću MOVX instrukcije. Razmjena se vrši bajtovima između akumulatora i vanjskog XSEG-a. XSEG ćeliji se može adresirati na dva načina: neizravno preko 16-bitnog pokazivača DPTR i stranično neizravno preko 8-bitnog pokazivača Ri, i=0,1. U potonjem slučaju, registar stranica je P2.

Neadresirane PUSH i POP naredbe pružaju prijenos podataka

između DSEG, RSEG i SFR.

Naredba XCH exchange omogućuje dvosmjernu razmjenu bajtova, a XCHD naredba pruža niže tetrade bajt operanda.

Skupina uputa za aritmetičke operacije(Tablica A2.2) ko-

sadrži upute za Add ADD, Carry Add ADDC, Posuđivanje Oduzimanje SUBB, Povećanje i smanjenje za jedan INC i DEC, Decimalna korekcija pakiranog BCD Add, MUL množenje i DIV Dijeljenje. Operacije se izvode nad cijelim brojevima bez predznaka. U operacijama zbrajanja i oduzimanja, akumulator je prvi operand i odredište rezultata. Za definiranje drugog operanda koriste se izravni registar, izravno apsolutno, izravno i neizravno adresiranje. INC i DEC operacije primjenjuju se na akumulator, izravno adresiran registar, izravno ili neizravno adresiranu memorijsku lokaciju. Osim toga, INC operacija se primjenjuje na sadržaj 16-bitnog registra pokazivača DPTR.

Cjelobrojno množenje i operacije dijeljenja bez predznaka uključuju akumulator i registar B. Množenjem se množi 8-bitna vrijednost A s 8-bitnom vrijednošću B i 16-bitni rezultat zapisuje u par BA. U ovom slučaju, registar B pohranjuje najviši dio proizvoda. Oznaka OV postavlja se ako je proizvod veći od 255. Kada se 8-bitna vrijednost A podijeli s 8-bitnom vrijednošću B, kvocijent se zapisuje u A, a ostatak u B. Pokušaj dijeljenja s 0 postavlja Zastavica preljeva OV.

Nakon naredbe za zbrajanje postavlja se naredba akumulatorske decimalne korekcije DA. Pojmovi moraju biti predstavljeni u BCD kodu. Korekcija se izvodi na standardni način.

Grupa logičkih instrukcija(Tablica A2.3 ) sadrži tri tipične operacije: ANL - logičko AND, ORL - logičko OR, XRL - logično isključivo OR. Izvor prvog operanda

je ili akumulator A ili izravno adresabilna memorijska ćelija. Drugi operand je specificiran jednom od četiri osnovne metode adresiranja. Grupa također uključuje pojedinačne operacije iznad sadržaja akumulatora: CLR - briše, CPL - inverzije, kao i RL, RLC, RR i RRC - operacije cikličkog i produženog pomaka udesno i ulijevo. To također uključuje operaciju razmjene tetrada u SWAP akumulatoru, što se može protumačiti kao ciklički pomak bajta za četiri bita.

Grupa uputa za rad s bitom(tablica A2.6) sadrži ko-

naredbe SETB - postaviti bit na 1, CLR - resetirati bit na 0, CPL - inverzija bita, ANL i ORL - logičko AND i logičko OR sadržaja zastavice C i izravno adresiranog bita, MOV - prosljeđivanje bita.

V U bitnim operacijama, zastavica C igra ulogu Booleovog akumulatora. Sadržaj C zastavice ili izravno adresiran bit BSEG područja koristi se kao operandi. U ANL i ORL operacijama možete koristiti sadržaj izravno adresiranog bita (bit) ili inverzni sadržaj (/bit).

V u ovu grupu spadaju i upute za uvjetno preskakanje s relativnom 8-bitni pomak rel. Uvjetna grana se može izvršiti ili kada je bit postavljen (JB naredba) ili obrisan (JNB naredba). Posebno treba istaknuti JBC instrukciju, koja, kada je bit postavljen, implementira granu i istovremeno resetira bit na 0.

Grupa naredbi za prijenos kontrole(Tablice A2.4 i A2.5)

drži bezuvjetne upute za skok AJMP, LJMP, SJMP, JMP, skoči uvjetno JZ, JNZ, CJNE, pozovi ACALL, LCALL, vrati RET, RETI i ažuriraj uvjetnim skokom DJNZ. Ovdje je također uključena prazna NOP naredba.

V Relativno adresiranje se naširoko koristi u naredbama prijenosa kontrole kako bi se omogućilo stvaranje premještavih programskih modula. Relativna adresa je 8-bitni pomak rel je potpisani bajt koji omogućuje prijelaz na (-128… +127) bajtova u odnosu na trenutnu poziciju računala. Ili izravna adresa addr16 ili neizravna @A+DPTR adresa može se koristiti za skok na bilo koju drugu točku u adresnom prostoru od 64 KB. U potonjem slučaju, sadržaj A se tumači kao cijeli broj bez predznaka. Uvedena je varijanta kratkog izravnog adresiranja addr11 unutar 2K trenutne stranice radi kompatibilnosti s obitelji MCS-48.

Sve ove vrste adresiranja koriste se u uputama za skok. Naredbe poziva koriste samo metode izravnog adresiranja addr16 i addr11 na stranici. Sve uvjetne naredbe koriste samo relativno adresiranje.

Kada mikrokontroler prepozna zahtjev za prekidom, izdaje instrukciju LCALL addr16, koja automatski pohranjuje povratnu adresu na stog. Informacije o stanju programa (sadržaj registra PSW) ne pohranjuju se automatski. Pri čemu

UDK 681.5, 681.325.5 (075.8)

BBK 32.973.202-018.2 i 73

Ščerbina A.N.Računalni strojevi, sustavi i mreže. Mikrokontroleri i mikroprocesori u upravljačkim sustavima: Cheb. dodatak / A.N. Shcherbina, P.A. Nechaev-SPb.: S Veleučilišta. un-ta, 2012.-226 str.

Odgovara sadržaju državnog obrazovnog standarda za područja izobrazbe i specijalnosti iz područja upravljanja u tehničkim sustavima, elektroenergetici i elektrotehnici i sadržaju oglednog nastavnog plana i programa discipline "Računala, sustavi i mreže".

Temeljna pitanja logičke organizacije mikroprocesorskih sustava razmatraju se na primjeru osnovne arhitekture obitelji mikrokontrolera MCS-51 tvrtke Intel. Opisana je tehnologija programiranja mikrokontrolera na jezicima Assembler i SI.

Može biti od koristi studentima i nastavnicima visokih tehničkih ustanova, stručnjacima za automatizaciju tehnoloških procesa i proizvodne opreme, kao i projektantima mikroprocesorskih sustava.

Odgovara i sadržaju državnog obrazovnog standarda disciplina "Mikrokontroleri i mikroprocesori u sustavima upravljanja" i "Elektronički uređaji automatike" za prvostupničko, inženjersko i magistarsko izobrazbu smjera 140400 "Elektroenergetika i elektrotehnika".

Objavljeno odlukom uredničkog i izdavačkog vijeća

Državno politehničko sveučilište u Sankt Peterburgu.

© Shcherbina A. N., Nechaev P. A., 2012

© Država Sankt Peterburg

Veleučilište, 2012

ISBN 978-5-7422-3553-8

Uvod.. 7

Poglavlje 1. Arhitektura obitelji MCS51. 10

1.1 Opće karakteristike 10

1.2 Blok dijagram 11

1.3 Dodjela pinova mikrokontrolera 8051 15

1.4 Organizacija memorije 17

1.4.1 Programska memorija (ROM) 18

1.4.2 Memorija podataka (RAM) 19

1.4.3 Registri posebnih funkcija. dvadeset

1.4.4 Registar zastave (PSW) 23

1.5 Uređaj za upravljanje i sinkronizaciju 26

1.6 Organiziranje I/O portova 27

1.6.1 Opći podaci. 27

1.6.2 Alternativne funkcije. 27

1.7. Tajmeri / brojači mikrokontrolera iz obitelji 8051. 28

1.7.1. Struktura mjerača vremena. 28

1.7.2 Načini rada mjerača vremena. trideset

1.8. Serijski port 32

1.8.1. Struktura serijskog porta. 32

1.8.2. Registar upravljanja/statusa primopredajnika SCON.. 34

1.8.3. Registar kontrole snage PCON.. 36

1.9. Sustav prekida 37

1.9.1. Struktura sustava prekida. 37

1.9.2 Izvršavanje rutine prekida. 40

Poglavlje 2 Značajke 80C51GB.. mikrokontrolera 42

2.1 Značajke 42

2.2 I/O portovi P0-P5 43

2.2.1 Rad I/O portova. 43

2.2.2 Pisanje na port.. 46

2.3 Značajke 8XC51GB.. sustava prekida 49

Omogući/onemogući prekide. 50

Upravljanje prioritetom prekida. 51

vanjski prekidi. 54

2.3. ADC čvor 56

2.4. Hardverski nadzornik 61

2.5. Detekcija kvara sata 63

2.6. Matrica programabilnih brojača RSA 64

2.6.1. Struktura PCA.. 64

2.6.2. PCA registar načina rada brojača (CMOD) 66

2.6.3. Kontrolni registar PCA brojača (CON) 67

2.6.4. Usporedite/popravite module. 68

2.7. Poboljšani serijski port 76

2.8. Brojači vremena 79

Dodjela pinova 8XC51GB.. grupnih mikrokontrolera 86

Poglavlje 3 Programiranje MK 8051GB.. 89

3.1. Model softvera 89

3.2 Tipovi podataka 93

3.3 Načini adresiranja podataka 93

3.4 Sustav zapovijedanja 95

3.4.1 Opće karakteristike. 95

3.4.2 Vrste naredbi. 96

3.4.3 Vrste operanda. 97

3.4.4 Naredbe za prijenos podataka mikrokontrolera. 98

3.4.5 Aritmetičke upute 8051.101

3.4.6 8051 Logičke naredbe MCU. 104

3.4.7 8051 Bit Operation Commands. 106

3.5 Programi za otklanjanje pogrešaka 111

Poglavlje 4. Programski jezik ASM-51. 112

4.2 Pisanje teksta programa 113

4.3 Jezična abeceda. 114

4.4 Identifikatori. 115

4.5 Brojevi 117

4.6 Direktive 118

4.7 Implementacija potprograma u ASM51 122

4.7.1 Struktura potprograma-procedure u jeziku ASM51. 122

4.7.2 Prosljeđivanje parametarskih varijabli u potprogram. 123

4.7.3 Implementacija potprograma-funkcija u jeziku ASM51. 123

4.7.4 Implementacija rutina za rukovanje prekidima u jeziku ASM51. 124

4.8 Strukturirano programiranje u asemblerskom jeziku. 125

4.9 Osobitosti prevođenja višemodulnih programa.. 126

4.10 Korištenje segmenata 128

4.10.1 Particioniranje MK memorije na segmente .. 128

4.10.2 Apsolutni memorijski segmenti. 129

4.10.2 Premještavi memorijski segmenti. 131

Poglavlje 5. Programski jezik C-51. 134

5.1 Opće karakteristike jezika 134

5.3 Struktura programa C-51 136

5.3. Elementi programskog jezika C-51 138

5.3.1. Simboli.. 138

5.3.2. Leksičke jedinice, separatori i upotreba razmaka. 141

5.3.3 Identifikatori.. 142

5.3.4 Ključne riječi. 143

5.3.5 Konstante.. 143

5.4. Izrazi u jezičnim izjavama 146

programiranje C-51 146

5.5. Prioriteti operacije 148

5.6. Izjave programskog jezika C-51 149

5.6.1. operatori deklaracije. 150

5.6.2 Izvršni izrazi.. 150

5.6.3 Operator dodjele. 151

5.6.4 Uvjetna izjava. 151

5.6.5 Strukturni operator (). 152

5.6.6 Naredba petlje for. 152

5.6.7 Naredba petlje s provjerom uvjeta do tijela while petlje. 153

5.6.8 Naredba petlje s provjerom uvjeta nakon tijela petlje do while. 154

5.6.9 Izjava o prekidu. 155

5.6.10 Izjava o nastavku. 155

5.6.11 Izjava o odabiru prekidača. 155

5.6.12 Operator goto. 157

5.6.13 Operatorski izraz. 158

5.6.14 Naredba povrata iz potprograma return. 158

5.6.15 Prazna izjava. 158

5.7. Deklariranje varijabli u programskom jeziku C-51. 159

5.7.1. Deklaracija varijable. 159

5.7.3 Cjelobrojni tipovi podataka. 161

5.7.4 Brojevi s pomičnim zarezom. 162

5.7.5 Varijable nabrojanog tipa. 162

5.7.6. Deklariranje nizova u programskom jeziku C-51. 164

5.7.7. Konstrukcije.. 165

5.7.8. Asocijacije (mješavine) 166

5.8. Korištenje pokazivača u C-51 167

5.8.1. Deklariranje pokazivača. 167

5.8.2. Neupisani pokazivači. 168

5.8.3. Pokazivači ovisni o memoriji. 169

5.9. Deklariranje novih tipova varijabli 169

5.10. Inicijalizacija podataka 170

5.11. Korištenje potprograma u programskom jeziku C-51. 170

5.11.1. Definicija potprograma.. 171

5.11.2. Parametri potprograma .. 173

5.11.3. Unaprijed deklaracija potprograma.. 174

5.11.4 Pozivanje potprograma.. 176

5.11.5 Rekurzivni poziv potprograma.. 176

5.11.6 Prekidane rutine. 177

5.11.7 Opseg varijabli i potprograma.. 178

5.12. Višemodulni programi 179

Poglavlje 6. Priprema programa u integriranom razvojnom okruženju Keil μVision2. 182

6.1 Izrada projekta ASM-51 182

6.2 Primjer izrade C projekta za kontroler obuke u Keil μVision2 IDE 188

Poglavlje 7 Opis kontrolera učenja .. 199

7.1. Struktura kontrolera 199

7.2. Adresni prostor 200

7.2.1. Dodjela memorije. 200

7.2.2 Vanjska memorija. 201

7.2.3. Interna memorija podataka. 202

7.3. Dodjela ulazno/izlaznih portova 202

7.4. Serijski priključak……………………………………………203

7.5. Rad s LCD 205

7.6. Kontrolne ploče……………………………………………………………213

DODATAK P2 STRUKTURA IZVJEŠĆA O LABORATORIJSKOM RADU……..217

Dodatak P3 Kodovi strojnih naredbi. 217

Literatura... 224

Uvod

U razvoju specijalnosti vezanih uz automatizaciju tehnoloških procesa i proizvodnje, studij mikrokontrolera jedan je od važnih odjela.

U svijetu postoji kontinuirani razvoj i pojava sve više 16- i 32-bitnih mikrokontrolera i mikroprocesora, no najveći udio na svjetskom tržištu mikroprocesora i dalje pripada 8-bitnim uređajima. Prema svim prognozama analitičkih tvrtki za bližu budućnost, vodeći položaj 8-bitnih mikrokontrolera na svjetskom tržištu će se nastaviti.

Trenutno, među svim 8-bitnim mikrokontrolerima, obitelj MCS-51 je neprikosnoveni lider u broju varijanti i broju tvrtki koje proizvode njegove modifikacije. Ime je dobio po prvom predstavniku ove obitelji - mikrokontroleru 8051. Uspješan set perifernih uređaja, fleksibilan izbor vanjske ili interne programske memorije i pristupačna cijena osigurali su uspjeh ovog mikrokontrolera na tržištu.

Prednosti obitelji MCS-51:

arhitektura, koja je de facto standard;

Ekstremna širina obitelji i raznolikost mogućnosti;

Dostupnost visokoučinkovitih i proširenih verzija procesora;

značajan broj slobodno dostupnih softverskih i hardverskih razvoja;

jednostavnost hardverskog programiranja, uključujući programiranje unutar kruga;

niska cijena i dostupnost osnovnih čipova;

Dostupnost specijaliziranih verzija kontrolera za posebne uvjete korištenja

Dostupnost verzija kontrolera sa smanjenom razinom elektromagnetskih smetnji;

· široka popularnost među programerima starije generacije, kako u svijetu tako iu zemljama ZND-a;

Podrška arhitekturi od strane vodećih obrazovnih institucija svijeta.

I, konačno, glavna prednost: svladavši osnovni čip obitelji, lako je početi raditi s takvim računalnim "čudovištima" kao što su Cygnal, Dallas Semiconductor, Analog Devices, Texas Instruments mikrokontroleri.

Obitelj MCS-51 uključuje cijeli niz mikro krugova od najjednostavnijih mikrokontrolera do prilično složenih. Do danas postoji više od 200 modifikacija mikrokontrolera obitelji 8051, koje proizvodi gotovo 20 tvrtki. Svake godine postoji sve više varijanti predstavnika ove obitelji.

Glavna područja razvoja su:

povećanje brzine (povećanje frekvencije takta i redizajn arhitekture);

smanjenje napona napajanja i potrošnje energije;

· povećanje količine RAM-a i FLASH memorije na čipu uz mogućnost programiranja unutar kruga;

· uvođenje složenih uređaja kao što su sustavi upravljanja pogonom, CAN i USB sučelja itd. na periferiju mikrokontrolera.

Mikrokontroleri iz obitelji MCS-51 omogućuju vam obavljanje zadataka upravljanja raznim uređajima i implementacije pojedinačnih čvorova analognog kruga. Svi mikro krugovi ove obitelji rade s istim sustavom zapovijedanja. Većina ih se izvodi u istim kućištima s istim pinoutom (numeracija nogu za kućište). To omogućuje korištenje mikro krugova različitih proizvođača za razvijeni uređaj bez mijenjanja dijagrama sklopa uređaja i programa.

Glavni proizvođači sorti 51. obitelji u svijetu su Philips, Siemens, Intel, Atmel, Dallas, Temic, Oki, AMD, MHS, Gold Star, Winbond, Silicon Systems i niz drugih.

Karakteristike analoga mikrokontrolera obitelji MCS-51 (Intel 8XC51FA, 8XC51GB, 80C152) s naprednim značajkama dane su u tablici. U 1.

Tablica B.1

| radna memorija | ROM | SAR | ADC | WDT | T/C | Posteljica. Kanali | Osobitosti | |

| Atmel: AT89C2051 | ||||||||

| - | - | - | - | UART | Flash 2 Kb | |||

| AT89C4051 | - | - | - | - | UART | Flash 4 Kb | ||

| AT89S4D12 | 128 tisuća | - | - | - | UART, SPI | Flash 4 Kb | ||

| DALLAS Semiconductor: DS5000FP | ||||||||

| - | - | - | + | UART | bootstrap loader | |||

| DS5001FP | - | - | - | + | UART | bootstrap loader | ||

| DS8xC520 | 16 tisuća | - | - | + | 2xUART | 2DPTR | ||

| SIEMENS: C505C | ||||||||

| 16 tisuća | - | + | + | UART, KAN | 8DPTR | |||

| C515C | 64 tisuća | - | + | + | UART+SSC+CAN | 4 PWM, 8 DPTR | ||

| Philips: *89C51RA+ | ||||||||

| - | + | - | + | UART | 2 DPTR, 4. nivo prekid, clock out, Flash 8K | |||

| P51XAG1x | 8K | - | - | + | 2 UART-a | |||

| Intel: 8xC51RA | ||||||||

| 8K | - | + | + | UART | 4 razine IRQ, clock out | |||

| 8XC196KC | 64 tisuća | 16 tisuća | - | + | - | UART | 3 PWM | |

| 80C196KB | 64 tisuća | 8K | - | + | - | UART | PWM |

Poglavlje 1 Obiteljska arhitektura MCS51

8-bitni mikrokontroleri s jednim čipom iz obitelji MCS-51 stekli su veliku popularnost među programerima mikroprocesorskih upravljačkih sustava zbog svoje dobro osmišljene arhitekture. Arhitektura mikrokontrolera je skup internih i eksternih softverski dostupnih hardverskih resursa i sustava naredbi. Arhitektura obitelji MCS-51 uvelike je određena njegovom svrhom - izgradnjom kompaktnih i jeftinih digitalnih uređaja. Mikrokontroleri koji obavljaju sve funkcije mikroračunala pomoću jednog mikrosklopa nazivaju se računala s jednim čipom (OEVM).

Intel je izdao oko 50 modela baziranih na operativnoj jezgri mikrokontrolera Intel 8051. Istovremeno, mnoge druge tvrtke, poput Atmela, Philipsa, započele su proizvodnju svojih mikrokontrolera razvijenih u standardu MCS-51.

Opće karakteristike

Glavne karakteristike obitelji:

· 8-bitna središnja procesorska jedinica (CPU), usmjerena na kontrolu izvršnih uređaja;

· CPU ima ugrađeni sklop 8-bitnog hardverskog množenja i dijeljenja brojeva;

Prisutnost u skupu instrukcija velikog broja operacija za rad s izravno adresiranim bitovima omogućuje govoriti o procesoru za rad s bitnim podacima (Booleov procesor);

interna (na čipu) programska memorija maske ili reprogramibilnog tipa, koja ima volumen od 4 do 32 Kb za različite kristale, u nekim verzijama je odsutna;

· najmanje 128 bajtova rezidentnog RAM-a koji se koristi za organizaciju, registar banaka, stog i pohranu korisničkih podataka;

· najmanje 32 dvosmjerne linije sučelja (porta), pojedinačno konfigurirane za unos ili izlaz informacija;

· dva 16-bitna multi-mode brojača/tajmera koji se koriste za brojanje vanjskih događaja, organiziranje vremenskih kašnjenja i satiranje komunikacijskog porta;

· Dvosmjerni dupleks asinkroni primopredajnik (UART) dizajniran za organiziranje komunikacijskih kanala između mikrokontrolera i vanjskih uređaja sa širokim rasponom brzina prijenosa informacija. Postoje sredstva za hardversko-softversku integraciju mikrokontrolera u povezani sustav;

· dvorazinski prioritetni sustav prekida koji podržava najmanje 5 vektora prekida iz 4 interna i 2 vanjska izvora događaja;

ugrađeni generator takta.

Strukturna shema

Blok dijagram kontrolera prikazan je na slici 1.1 i sastoji se od sljedećih glavnih funkcionalnih jedinica: upravljačke jedinice, aritmetičko-logičke jedinice, jedinice timera/brojila, serijskog sučelja i jedinice za prekid, programskog brojača, memorije podataka i programska memorija. Bilateralna razmjena provodi se pomoću interne 8-bitne autoceste podataka. Gotovo svi predstavnici obitelji MCS-51 izgrađeni su prema ovoj shemi. Različiti mikro krugovi ove obitelji razlikuju se samo po registrima posebne namjene (uključujući broj priključaka).

Jedinica za upravljanje i sinkronizaciju (Timing and Control)- dizajniran za generiranje sinkronizirajućih i upravljačkih signala koji osiguravaju koordinaciju zajedničkog rada OEVM jedinica u svim dopuštenim načinima rada. Upravljačka jedinica uključuje:

uređaj za formiranje vremenskih intervala;

ulazno-izlazna logika;

registar uputa;

registar upravljanja potrošnjom električne energije;

dekoder naredbi, računalna upravljačka logika.

Riža. 1.1. Strukturni dijagram I8051 kontrolera.

Uređaj za određivanje vremena namijenjen je za generiranje i izlaz internih sinkronizacijskih signala faza, ciklusa i ciklusa. Broj strojnih ciklusa određuje trajanje izvršenja instrukcije. Gotovo sve OEVM naredbe izvode se u jednom ili dva strojna ciklusa, osim naredbi za množenje i dijeljenje čije trajanje je četiri strojna ciklusa. Označimo frekvenciju glavnog oscilatora kroz F g. Trajanje strojnog ciklusa je 12/F g, odnosno 12 perioda signala glavnog oscilatora. Ulazno-izlazna logika je dizajnirana za primanje i izdavanje signala koji osiguravaju razmjenu informacija s vanjskim uređajima kroz ulazno/izlazne portove P0-P3.

Zapovjedni registar dizajniran je za snimanje i pohranjivanje 8-bitnog operacijskog koda naredbe koja se izvršava. Operativni kod se uz pomoć dekodera naredbi i računalne upravljačke logike pretvara u mikroprogram za izvršavanje naredbi.

Registar kontrole potražnje (PCON) omogućuje vam da zaustavite rad mikrokontrolera kako biste smanjili potrošnju energije i smanjili razinu smetnji od mikrokontrolera. Još veće smanjenje potrošnje energije i smanjenje buke može se postići zaustavljanjem glavnog oscilatora mikrokontrolera. To se može postići prebacivanjem bitova u registru upravljanja potražnjom PCON. Za n-MOS proizvodnu opciju (serija 1816 ili strani čipovi koji nemaju slovo "c" u sredini imena), PCON registar kontrole snage sadrži samo jedan bit koji kontrolira brzinu prijenosa SMOD serijskog porta, i nema bitova za kontrolu snage.

Aritmetičko-logička jedinica (ALU) je paralelni osmobitni uređaj koji pruža aritmetičke i logičke operacije. ALU se sastoji od:

registri akumulatora, registri držanja TMP1 i TMP2;

ROM konstante;

guja;

dodatni registar (registar B);

baterija (ACC);

registar statusa programa (PSW).

Registar registri akumulatora i držanja- osmobitni registri dizajnirani za primanje i pohranjivanje operanada za vrijeme trajanja operacija na njima. Ovi registri nisu programski dostupni.

ROM konstante osigurava razvoj ispravljačkog koda za binarno-decimalni prikaz podataka, koda maske za bitne operacije i konstantnog koda.

Paralelni 8-bitni zbrajač je sklop kombiniranog tipa sa sekvencijalnim prijenosom, dizajniran za izvođenje aritmetičkih operacija zbrajanja, oduzimanja i logičkih operacija zbrajanja, množenja, neekvivalencije i identičnosti.

Registar B- osmobitni registar koji se koristi tijekom operacija množenja i dijeljenja. Za ostale upute može se smatrati dodatnim registrom scratchpad-a.

Baterija- osmobitni registar dizajniran za primanje i pohranjivanje rezultata dobivenog prilikom izvođenja aritmetičko-logičkih operacija ili operacija pomaka

Serijsko sučelje i blok prekida (SIP) dizajniran za organizaciju ulaza – izlaza sekvencijalnih tokova informacija i organizaciju sustava programskih prekida. Blok uključuje:

tampon PIP;

logika upravljanja;

kontrolni registar;

međuspremnik odašiljača;

međuspremnik prijemnika;

serijski primopredajnik;

registar prioriteta prekida;

registar omogućavanja prekida;

logika obrade zastavice prekida i shema generiranja vektora.

Brojač programa je dizajniran da formira trenutnu 16-bitnu adresu interne programske memorije i 8/16-bitnu adresu vanjske programske memorije. Programski brojač sastoji se od 16-bitnog PC međuspremnika, PC registra i inkrementnog kruga (povećava sadržaj za 1).

Podatkovna memorija (RAM) namijenjen je za privremeno pohranjivanje informacija koje se koriste tijekom izvođenja programa.

Priključci P0, P1, P2, P3 su kvazi-dvosmjerni ulazno-izlazni portovi i dizajnirani su da osiguraju razmjenu informacija između OEVM-a i vanjskih uređaja, tvoreći 32 ulazno-izlazne linije.

Registar statusa programa (PSW) dizajniran je za pohranu informacija o stanju ALU-a tijekom izvođenja programa.

Programska memorija (EPROM) dizajniran za pohranjivanje programa i memorija je samo za čitanje (ROM). Različiti mikro krugovi koriste maskirane, UV-izbrisive ili FLASH ROM-ove.

Registar pokazivača podataka (DPTR) dizajniran za pohranu 16-bitne adrese vanjske memorije podataka.

Pokazivač steka (SP) je osmobitni registar dizajniran za organiziranje posebnog memorijskog područja podataka (stog), u koji možete privremeno pohraniti bilo koju memorijsku ćeliju.

1.3 8051 dodjela pinova mikrokontrolera(slika 1.2)

· U ss - potencijal zajedničke žice ("zemlja");

U cc - napon glavnog napajanja +5 V;

· X1,X2 - zaključci za spajanje kvarcnog rezonatora;

· RST - ulaz za opće resetiranje mikrokontrolera;

PSEN - dopuštenje vanjske programske memorije, izdano samo pri pristupu vanjskom ROM-u;

· ALE - eksterna memorijska adresa strobe;

· EA - onemogućiti internu memoriju programa; razina 0 na ovom ulazu uzrokuje da mikrokontroler izvršava program samo iz vanjskog ROM-a; ignoriranje unutarnjeg (ako potonje postoji);

Riža. 1.2. Dodjela pinova 8051.

P1 - osmobitni kvazi-dvosmjerni ulazno/izlazni port, svaki bit porta može se programirati i za unos i za izlaz informacija, bez obzira na status ostalih bitova;

· P2 - osmobitni kvazi-dvosmjerni port, sličan P1, pinovi ovog porta se koriste za izdavanje informacija o adresi prilikom pristupa vanjskoj programskoj ili podatkovnoj memoriji (ako se koristi 16-bitno adresiranje potonje). Osim toga, pinovi porta se koriste prilikom programiranja za unos bitova višeg reda adrese u mikrokontroler;

· RZ - osmobitni kvazi-dvosmjerni port, sličan R1, pinovi ovog porta mogu obavljati niz alternativnih funkcija koje se koriste u radu mjerača vremena, serijskog I/O porta, kontrolera prekida i eksternih memorija programa i podataka;

· P0 - multipleksirani osmobitni dvosmjerni port za ulaz-izlaz informacija, kroz ovaj port u različitim vremenskim trenucima izlaze niži bajt adrese i podataka.

Organizacija memorije

Cijela serija MCS-51 ima harvardsku arhitekturu, odnosno odvojene adresne prostore programske i podatkovne memorije. Struktura memorije prikazana je na sl. 1.3.

Količina interne (rezidentne) programske memorije (ROM, EPROM ili OTP ROM) koja se nalazi na čipu, ovisno o vrsti mikrosklopa, može biti 0 (ROMless), 4K (osnovni čip), 8K, 16K ili 32K. Ako je potrebno, korisnik može proširiti memoriju programa instaliranjem vanjskog ROM-a. Pristup unutarnjem ili vanjskom ROM-u određen je vrijednošću signala na pinu EA (External Access):

EA=V cc (napon napajanja) - pristup internom ROM-u;

EA=V ss (potencijal uzemljenja) - pristup vanjskom ROM-u.

Za čipove bez ROM-a, EA pin mora biti trajno spojen na V ss.

|  |

Riža. 1.3. Organizacija memorije obitelji MCS-51

Eksterni ROM čitač - (Program Store Enable) generira se prilikom pristupa vanjskoj programskoj memoriji i neaktivan je tijekom pristupa ROM-u koji se nalazi na čipu. Adresno područje niske programske memorije koristi sustav prekida. Arhitektura osnovnog čipa 8051 podržava pet izvora prekida:

dva vanjska prekida;

dva prekida od mjerača vremena;

prekida iz serijskog porta.

Na sl. 1.4 prikazuje mapu donjeg područja programske memorije.

Riža. 1.4. Karta donjeg područja programske memorije

Programska memorija (ROM)

Za mikrokontrolere iz obitelji 8051, programska memorija i memorija podataka su neovisni i neovisni uređaji kojima se adresiraju različite naredbe i upravljački signali.

Količina ugrađene programske memorije koja se nalazi na čipu mikrokontrolera 8051 je 4 KB (u obitelji do 32). Prilikom pristupa vanjskoj programskoj memoriji, svi 8051 mikrokontroleri uvijek koriste 16-bitnu adresu, što im omogućuje pristup 64 KB ROM-a. Mikrokontroler pristupa programskoj memoriji prilikom čitanja opkoda i operanada (pomoću računalnog programskog brojača), kao i prilikom izvršavanja naredbi za kopiranje bajta iz programske memorije u akumulator. Prilikom izvršavanja naredbi za kopiranje podataka, adresiranje programske memorijske ćelije iz koje će se podaci čitati može se provesti i korištenjem računala računala i posebnog dvobajtnog registra pokazivača podataka DPTR.

Podatkovna memorija (RAM)

Količina podatkovne memorije na čipu je 128 bajtova. Vanjska podatkovna memorija može biti do 64 KB. Prva 32 bajta organizirana su u četiri banke registara opće namjene, označene kao banka 0 - banka 3. Svaki od njih se sastoji od osam registara R0-R7. Programu je u svakom trenutku dostupna, uz adresiranje registra, samo jedna banka registara, čiji se broj nalazi u trećem i četvrtom bitu riječi statusa PSW programa.

8051 Adrese područja bitova mikrokontrolera

Tablica 1.1

| Adresa bajta (hex) | Bit adrese po bit | |||||||

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

| 2F | 7F | 7E | 7D | 7C | 7B | 7A | ||

| 2E | ||||||||

| 2D | 6F | 6E | 6D | 6C | 6B | 6A | ||

| 2C | ||||||||

| 2B | 5F | 5E | 5D | 5C | 5B | 5A | ||

| 2A | ||||||||

| 4F | 4E | 4D | 4C | 4B | 4A | |||

| 3F | 3E | 3D | 3C | 3B | 3A | |||

| 2F | 2E | 2D | 2C | 2B | 2A | |||

| 1F | 1E | 1D | 1C | 1B | 1A | |||

| 0F | 0E | 0D | 0C | 0B | 0A | |||

| 20h |

Preostali adresni prostor programer može konfigurirati prema vlastitom nahođenju: može prihvatiti područja stog, sustava i korisničkih podataka. Podatkovnim memorijskim ćelijama može se pristupiti na dva načina. Prvi način je izravno adresiranje memorijske ćelije. U ovom slučaju, adresa ćelije je operand odgovarajuće instrukcije. Druga metoda je neizravno adresiranje pomoću registara pokazivača R0 ili R1: prije izvršavanja odgovarajuće naredbe, jedan od njih mora sadržavati adresu ćelije kojoj je potrebno pristupiti.

Za pristup vanjskoj memoriji podataka koristi se samo neizravno adresiranje pomoću registara R0 i R1 ili pomoću 16-bitnog registra pokazivača DPTR.

Dio memorije podataka je područje bitova, ima mogućnost korištenja posebnih bitnih naredbi za adresiranje svake znamenke memorijskih ćelija. Adresa bitova koji se mogu izravno adresirati također se može napisati u obliku (ByteAddress).(Bit). Korespondencija između ove dvije metode adresiranja može se odrediti iz tablice. 1.1.

Ministarstvo općeg i strukovnog obrazovanja Ruske Federacije Novosibirsko državno tehničko sveučilište V.N. Veprik, V.A. Afanasiev, A.I. Druzhinin, A.A. Zemskov, A.R. Isaev, O.V. Malyavko MIKROKONTROLERI OBITELJI MCS-51 Udžbenik za kolegije "Mikroprocesorski sustavi" i "Projektiranje mikroprocesorskih sustava" za studente viših razreda Fakulteta automatizacije i računalnog inženjerstva svih oblika obrazovanja Novosibirsk 1997. V.N. Veprik, V.A. Afanasiev, A.I. Druzhinin, A.A. Zemskov, A.R. Isaev, O.V. Malyavko. Mikrokontroleri iz obitelji MCS-51: Tutorial. - Novosibirsk. Predloženi udžbenik sadrži opći opis arhitekture, funkcionalnosti i naredbenog sustava obitelji mikrokontrolera s jednim čipom (Embedded Microcontrollers) MCS-51, proizvođača INTEL. U drugom dijelu priručnika opisan je edukacijski mikroprocesorski kontroler UMPC-51 koji se nudi studentima kao predmet proučavanja pri izvođenju ciklusa laboratorijskog rada. Materijal priručnika može se koristiti u izradi kolegija i diploma, a može biti koristan i za stručne inženjere uključene u razvoj i rad elektroničke opreme. Autori izražavaju duboku zahvalnost CJSC-u "Nove Technologies", službenom distributeru INTEL-a, za pružanje materijala na temelju kojih je ovaj posao izveden. Tablica 15, ilustr. 25, popis lit. 12 naslova Recenzenti: E.D. Baran, G.G. Matuškin. Rad je pripremljen na Odjelu za računalno inženjerstvo Novosibirsk State © Tehničko sveučilište 2 UVOD. Obitelj 8-bitnih mikrokontrolera s jednim čipom MCS-51 pojavila se na svjetskom tržištu početkom osamdesetih. Prve modifikacije kristala (oko 7) izrađene su korištenjem visokokvalitetne n-MOS (HMOS) tehnologije i funkcionalno su dovršena mikroračunala s jednim čipom harvardske arhitekture, čiji je jedan od glavnih principa logično razdvajanje programa i podataka. memorijski adresni prostori. Razvojem poluvodičke tehnologije počele su se proizvoditi sljedeće verzije mikrosklopova MCS-51 korištenjem naprednije CMOS (CHMOS) tehnologije male snage (u aktivnom načinu rada potrošnja kristala je povećana na 10 50 mA). Naredbeni sustav MCS-51, usmjeren na implementaciju različitih algoritama digitalnog upravljanja, uz zadržavanje neke vanjske sličnosti sa sustavom zapovijedanja prethodne obitelji MCS-48, kvalitativno se proširio, ima temeljne inovacije: bit-orijentirane operacije i bitna polja adresabilna u memoriji podataka, što je omogućilo da se govori o implementaciji bitnog procesora na čipu; implementirano izvršavanje naredbi množenja, dijeljenja i oduzimanja; poboljšan rad sa stogom; proširena je grupa naredbi za prijenos kontrole; Sustav zapovijedanja počeo je izgledati simetričnije, odnosno manje ovisan o prijenosu podataka kroz bateriju. Funkcionalnost ugrađenih perifernih uređaja također je proširena uvođenjem: dva 16-bitna brojača vremena; hardverski serijski duplex port; sustav prekida na dvije razine; četiri 8-bitna I/O porta. Temeljne promjene u strukturi vremenskog ciklusa procesora dovele su do bržeg rada s vanjskom programskom i podatkovnom memorijom, kao i odgovora na vanjske i interne prekide. Ukupna veličina adresnog prostora vanjske programske i podatkovne memorije povećana je na 128 KB. 16-bitni registri programskog brojača (Program Counter) i pokazivača podataka (Data Pointer) omogućili su izravan pristup cijelom rasponu adresa, što je programerima dalo mogućnost implementacije algoritama za brzu obradu velikih nizova podataka. Svi softverski dostupni čvorovi mikrokontrolera svedeni su na posebno područje memorije podataka (Special Function Register), što im je omogućilo pristup na gotovo isti način kao i običnim ćelijama rezidentnog RAM-a. U kasnijim modifikacijama kristala, poboljšanje je išlo putem povećanja dodatne funkcionalnosti uz zadržavanje pune softverske kompatibilnosti s ranijim verzijama. Značajke najnovijih modifikacija mikrokontrolera obitelji MCS-51 su: potpuno statičan dizajn; 3- i 5-voltne verzije kristala; širok raspon ugrađenih perifernih uređaja; maksimalna frekvencija takta - 24 MHz; za pojedine skupine kristala - 33 MHz. Trenutno, MCS-51 uključuje oko 60 verzija kristala, osim toga, dostupna je i dostupna detaljna vlasnička dokumentacija (nažalost, još nije prevedena na ruski). Za pripremu softvera za mikrokontrolere MCS-51 uglavnom se koriste jezici ASM-51, C, za koje postoji niz prilično dobro dokazanih kompajlera, knjižnica standardnih potprograma i softverskih emulatora koje proizvode razne strane i domaće tvrtke. . 3 Unatoč dovoljnoj "starini" obitelji (više od 15 godina) i pojavi na svjetskom tržištu posljednjih godina jednočipnih mikrokontrolera većih performansi i poboljšane arhitekture - MCS-51, MCS-251, MCS-96, MCS-51 kontroleri će se dugo koristiti u širokoj upotrebi u relativno jednostavnim ugrađenim upravljačkim sustavima. 4 1. INTEL SISTEM OZNAČAVANJA KOMPONENTI I FUNKCIONALNI SASTAV OBITELJI MCS-51 Za označavanje mikročipova, INTEL koristi sustav označavanja koji se sastoji od nekoliko polja: , automobilska verzija za prošireni temperaturni raspon (-40 / +125 C) M (vojno) , verzija prema vojnim standardima (-55 / +125 C) Q ili C (Commercial), "komercijalni" temperaturni raspon (0 / +70 C ) sa (160 8) - satni dinamički toplinski trening; L ili E (Extended), "prošireni" temperaturni raspon (-40/+85 C) sa (160 8) satnim dinamičkim termičkim treningom; T (Extended), "prošireni" temperaturni raspon (-40/+85 C) bez termičke obuke; I (Industrijski), izvedba prema industrijskim standardima. Drugo polje sadrži jednoslovni ili dvoslovni prefiks koji označava vrstu paketa mikrosklopa (Package Type). Danas postoji nekoliko desetaka različitih vrsta paketa mikrosklopova, stoga ćemo, kao primjer, dati samo neke oznake: A Ceramic Pin Grid Array, (PGA); C Keramički dvostruki in-line paket, (CDIP); K Ceramic Quad Flatpack Package, (QFP); KD Plastic Quad Flatpack Package, Fine Pitch, Die Down, (PQFP); KU Plastic Quad Flatpack Package, Fine Pitch, Die Up, (PQFP); N Plastic Leaded Chip Carrier, (PLCC); P Plastični dvostruki in-line paket, (PDIP); SM jednostruki bezvodni memorijski modul, (SIMM); U Plastični dvostruki in-line paket, skupljajući se, (PDIPS); Z cik-cak in-line paket, (ZIP). Treće polje može sadržavati do 15 numeričkih i abecednih znakova koji označavaju vrstu određenog uređaja koji se nalazi na čipu. Četvrto polje može sadržavati do šest numeričkih i abecednih znakova, odražavajući različite značajke i verzije mikro krugova. Dodatne informacije o vrstama kućišta i njihovom dizajnu možete pronaći u knjizi: Broj narudžbe pakiranja 240800. S obzirom na opisane mikrokontrolere obitelji MCS-51, prvi znak trećeg polja tradicionalno je (za Intel) jednak "8". Drugi znak trećeg polja obično označava vrstu ugrađenog ROM-a: 0 programska maska ROM-a; ne-ROM kristal (za kasnije verzije kristala); 1 maska ROM programa (Standard ROM Code, Firmware); 3 maska ROM (za kasnije verzije kristala), (prilagodljivi ROM kod); 7 UFPROM ili jednokratni programabilni ROM (EPROM ili OTP ROM); 8 EEPROM (Flash - memorija na čipu) Zatim može slijediti slovo koje označava tehnološke značajke proizvodnje: bez slova HMOS tehnologija, napajanje od 5V; S CHMOS tehnologijom, napajanje od 5V; l CHMOS tehnologija, 3V napajanje; 5 Sljedeći znakovi trećeg polja za mikrokontrolere obitelji MCS-51 su brojevi (na primjer, 31,32,51,54,58,152) i od jednog do četiri slova koja odražavaju funkcionalne značajke čipova (npr. Veličina ROM-a, specifičnosti skupine čipova, prisutnost sustavne zaštite programske memorije od neovlaštenog pristupa, mogućnost korištenja naprednijeg programskog algoritma „Quick Pulse“ i slično). U originalnoj tehničkoj dokumentaciji tvrtke Intel, svi mikrokontroleri iz obitelji MCS-51 grupirani su u skupine ("Linija proizvoda"), od kojih svaka kombinira najbliže verzije kristala u smislu njihove funkcionalnosti i električnih parametara. Budući da se nazivi mikro krugova jedne skupine neznatno razlikuju, tada se za označavanje svake pojedinačne skupine koristi generalizirana simbolika, nastala od označavanja specifičnih mikro krugova, zamjenom različitih znakova s "X". Tako se mogu razlikovati sljedeće skupine mikrokontrolera. 1. Grupa 8X5X (linija proizvoda 8051 i linija proizvoda 8052): 8031AN, 8051AN, 8751H, 8051AHP, 8751H-8, 8751VN, 8032AN, 8052AN, 8752VN. 2. Grupa 8HS51 (linija proizvoda 80S51): 80S31VN, 80S51VN, 87S51. 3. Grupa 8HS5H (8HS52/54/58 linija proizvoda): 80S32, 80S52, 87S52, 80S54, 87S54, 80S58, 87S58. 4. Grupa 8XC51FX (8XC51FA/FB/FC linija proizvoda): 80C51FA, 83C51FA, 87C51FA, 83C51FB, 87C51FB, 83C51FC, 87C51FC. 5. Grupa 8XL5X (8XL52/54/58 linija proizvoda): 80L52, 87L52, 80L54, 87L54, 80L58, 87L58. 6. Grupa 8XL51FX (8XL51FA/FB/FC linija proizvoda): 80L51FA, 83L51FA, 87L51FA, 83L51FB, 87L51FB, 83L51FC, 87L51FC. 7. Grupa 8XC51RX (linija proizvoda 8XC51RA/RB/RC): 80C51RA, 83C51RA, 87C51RA, 83C51RB, 87C51RB, 83C51RC, 87C51RC. 8. Grupa 8XC51GB (linija proizvoda 8XC51GX): 80C51GB, 83C51GB, 87C51GB. 9. Grupa 8XC152JX (8XC152 linija proizvoda): 80C152JA, 83C152JA, 80C152JB, 80C152JC, 83C152JC, 80C152JD. 10. Grupa 8XC51SL (8XC51SL linija proizvoda): 80C51SL-BG, 81C51SL-BG, 83C51SL-BG, 80C51-AH, 81C51SL-AH, 83C51SL-AH, 87C51SL-AH, 80ALC51SL-5, 80ALC55-1, 81SLC5-1 87C51SL-AL. Prva skupina mikrokontrolera uključuje mlađe modele obitelji, izrađene korištenjem n-MOS tehnologije i ne preporučuju se za korištenje u novim razvojima, sve ostale skupine izrađene su korištenjem moderne CMOS tehnologije. Mikrokrugovi druge, treće i četvrte skupine danas su klasični predstavnici obitelji MCS-51. Peta i šesta skupina uključuju 3-voltne verzije kristala (niskonaponske). Kristali sedme skupine opremljeni su proširenim RAM-om (Expanded RAM), čiji je volumen 512 bajtova. Mikrokrugovi osme, devete i desete skupine su mikrokontroleri specijalizirani za primjenu (Application Specific). Mnoge današnje aplikacije zahtijevaju kontrolne mikrokontrolere visokih performansi koji koriste napredno adresiranje, arhitekturu registra, veliki interni RAM i prostor stog, te učinkovito podržavaju programiranje jezika visoke razine. Ovi mikrokontroleri uključuju mikrokontrolere Nove arhitekture iz obitelji MCS-5 i MCS-251, koje je Intel lansirao 1995. godine. Funkcionalni sastav i ključne značajke mikrokontrolera MCS-51/MCS-251 prikazani su u dodatku. 6 2. GLAVNE KARAKTERISTIKE OSNOVNOG MODELA OBITELJI MICROCONTROLLERA MCS-51. Osnovni model obitelji mikrokontrolera MCS-51 i osnova za sve naknadne modifikacije je mikrokontroler I-8051. Njegove glavne značajke su sljedeće: osmobitni CPU optimiziran za upravljačke funkcije; ugrađeni generator takta; adresni prostor programske memorije - 64 K; adresni prostor memorije podataka - 64 K; interna programska memorija - 4 K; interna memorija podataka - 128 bajtova; dodatne značajke za izvođenje operacija Booleove algebre (operacije po bitovima); 32 dvosmjerna i pojedinačno adresabilna I/O linije; 2 x 16-bitna višenamjenska mjerača vremena/brojila; full duplex asinkroni primopredajnik; vektorski sustav prekida s dvije razine prioriteta i šest izvora događaja. Blok dijagram I-8051 prikazan je na slici 1, a raspored pinova mikrosklopa prikazan je na slici 2. Vanjski prekidi Prekidi 128 bajtova T/C 0 brojač 4K ROM kontrola RAM T/C 1 ulazi CPU BUS 4 I/O Serijski OSC kontrolni portovi Port P0 P1 P2 P3 T D R D Adresa/podaci Slika 1. Blok dijagram I-8051 Cijela serija MCS-51 ima harvardsku arhitekturu, odnosno odvojene adresne prostore memorije programa i podataka. Organizacija memorije prikazana je na slici 3. Količina interne (rezidentne) programske memorije (ROM, EPROM ili OTP ROM) koja se nalazi na čipu, ovisno o vrsti mikrosklopa, može biti 0 (ROMless), 4K (osnovni čip), 8K, 16K ili 32K. Ako je potrebno, korisnik može proširiti memoriju programa instaliranjem vanjskog ROM-a. Pristup unutarnjem ili vanjskom ROM-u određen je vrijednošću signala na pinu EA (External Access): EA=Vcc (napon napajanja) - pristup internom ROM-u; EA=Vss (potencijal zemlje) - pristup vanjskom ROM-u. Za čipove bez ROM-a, EA pin mora biti trajno spojen na Vss. Eksterni ROM čitač - PS EN (Program Store Enable) generira se prilikom pristupa vanjskoj programskoj memoriji i nije aktivan tijekom pristupa ROM-u koji se nalazi na čipu. 7 Nisko područje programske memorije koristi sustav prekida, arhitektura 8051 čipa pruža podršku za pet izvora prekida: dva vanjska prekida; dva prekida od mjerača vremena; prekida iz serijskog porta. P1.0 1 40 Vcc P1.1 2 39 P0. 0 (AD0) P1.2 3 38 P0.1 (AD1) P1.3 4 37 P0.2 (AD2) P1.4 5 36 P0.3 (AD3) P1.5 6 35 P0.4 (AD4) P1. 6 7 34 P0.5 (AD5) P1.7 8 33 P0.6 (AD6) RESET 9 32 P0.7 (AD7) (RD) P3.0 10 31 EA/Vpp (TD) P3.1 11 30 ALE/ PROG (INT0) P3.2 12 29 PSEN (INT1) P3.3 13 28 P2.7 (A15) (T0) P3.4 14 27 P2.6 (A14) (T1) P3.5 15 26 P2.5 ( A13) (WR) P3.6 16 25 P2.4 (A12) (RD) P3.7 17 24 P2.3 (A11) XTAL2 18 23 P2.2 (A10) XTAL1 19 22 P2.1 (A9) Vss 20 21 P2.0 (A8) Sl.2. Dodjela pinova I-8051 Programska memorija (čitanje) Memorija podataka (čitanje/pisanje) FFFFH Vanjski ROM FFFFH Eksterni @DPTR RD memorija PSEN WR podaci @PC MOVC EA=0 Unutarnja memorija @DPTR podaci @PC vanjski unutarnji FFH gornji 128 SFR MOVX ROM ROM 80H EA=0 0000H EA=1 donji 128 00H 0000H PSEN Sl.3. Organizacija memorije obitelji MCS-51 8 Slika 4 prikazuje mapu donjeg područja programske memorije. ROM Programska memorija 0033H 002BH Serijski port 0023H Vektori Timer1 001BH prekida EINT1 0013H Timer0 000BH EINT0 0003H Početna adresa 0000H (Reset) Sl.4. Adrese vektora prekida u memoriji programa nalaze se u intervalima od 8 bajtova: - 0003H vanjski prekid 0 (External Interrupt 0) - izlaz IN T 0 ; - 000BH prekid od timera 0 (prema zastavici prelijevanja tajmera - T F 0); - 0013H vanjski prekid 1 (vanjski prekid 1) - izlaz IN T 1; - 001BH prekid od timera 1 (pomoću zastavice preljeva tajmera - T F 1); - 0023H prekid serijskog porta (serijski prekid = prekid prijema ili prekid prijenosa); itd. Memorija podataka je odvojena od programske memorije. U ovom području može se adresirati 64K vanjske RAM-a. Prilikom pristupa vanjskoj podatkovnoj memoriji, CPU mikrokontrolera generira odgovarajuće signale čitanja (RD) ili pisanja (WR), interakcija s internom podatkovnom memorijom vrši se na razini naredbe, dok se RD i W R signali ne generiraju. Vanjska programska memorija i vanjska memorija podataka mogu se kombinirati kombiniranjem RD i PS EN signala na logičan I način kako bi se proizveo strobosjek vanjske memorije (program/podatak). Donjih 128 bajtova interne podatkovne memorije (donjih 128) prisutni su na svim MCS-51 čipovima i prikazani su na slici 5. Prva 32 bajta su 4 banke (registarska banka) od 8 registara (R7...R0). Registri R0 i R1 u bilo kojoj banci mogu se koristiti kao neizravni adresni registri. 16 bajtova koji slijede banke registara tvore blok prostora koji se može adresirati u bitovima. MCS-51 skup instrukcija sadrži široku paletu bitnih operacija, a 128 bitova u ovom bloku se mogu izravno adresirati, a adrese se kreću od 00H do 7FH. Svi bajtovi u donjoj polovici memorije od 128 bajtova mogu se adresirati izravno ili neizravno. Gornja polovica RAM memorije od 128 bajta (gornja 128) nije prisutna u I-8051 čipu, ali je dostupna u 256-bajtnim RAM verzijama čipova. U ovom slučaju, područje "Gornje 128" dostupno je samo s neizravnim adresiranjem. Područje SFR (Registar posebnih funkcija) dostupno je samo uz izravno adresiranje. Postavljanje registara posebnih funkcija u SFR prostor prikazan je na sl.6. Oni uključuju registre portova, mjerače vremena, periferne kontrole i tako dalje. 9 7Fh 7h 7 HRH 7D 74H 75H 75H 74H 74H 74H 71H 71H 71H 71H 71H 71H 71H 71H 71H 71H 71H 0FH 0FH 0H 0H 0H 0H 07H 06H 05H 04H 03H 02H 01H 00H 1FH RB3 18H 17H RB2 10H 0FH RB1 08H 07H SP nakon RESETIRANJA 00H RB0(R7+R0) Sl.5. Donjih 128 bajtova interne RAM memorije. bitovsko adresiranje 8 bajtova F8H FFH F0H B F7H E8H EFH E0H ACC E7H D8H DFH D0H PSW D7H C8H CFH C0H C7H B8H IP BFH B0H P3 B7H A8H IE AFH A0H P2 A7H 98H 98H S P2 A7H 98H 98H 8H P2 A7H 98H 98H 8H 98H 98H 98H 8H DPH PCO 87H N 0/8 1/9 2/A 3/B 4/C 5/D 6/E 7/F Sl.6. Postavljanje registara posebnih funkcija u SFR prostor. Za 16 adresa u SFR prostoru moguće je i bajtsko i bitno adresiranje. Za registre koji se mogu adresirati na bit, heksadecimalna adresa završava s "0H" ili "8H". Bit adrese u ovom području imaju vrijednosti od 80H do FFH. Cijela serija kristala obitelji MCS-51 ima osnovni SFR set, kao u I-8051 čipu, koji se nalazi na istim adresama. Međutim, u kristalima, koji predstavljaju daljnji razvoj obitelji u SFR regiji, dodaju se novi registri za proširenje 10

Odabir programa za obradu GIS-a

Odabir programa za obradu GIS-a Proračun i analiza električnog kruga izmjenične struje

Proračun i analiza električnog kruga izmjenične struje Skenirajući sondni mikroskop Trenutno stanje i razvoj skenirajuće sondne mikroskopije

Skenirajući sondni mikroskop Trenutno stanje i razvoj skenirajuće sondne mikroskopije